一种基于CPLD的QDPSK调制解调电路设计

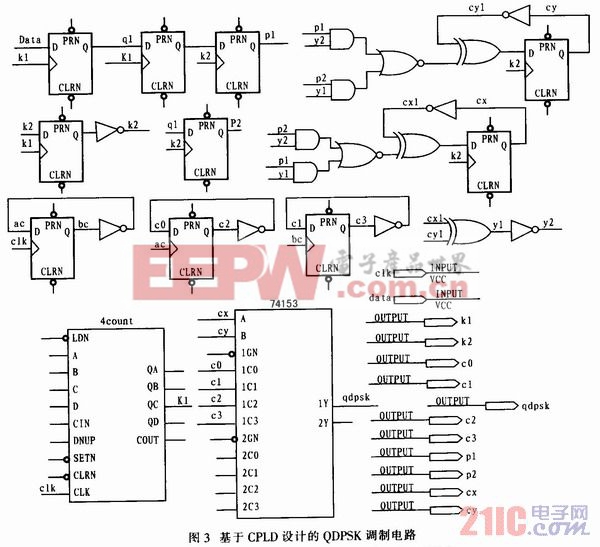

图3所示QDPSK调制电路引脚关系为:引脚k1表示数据时钟clk经过计数器4count的八分频输出,引脚k2表示数据时钟k1的二分频输出,引脚ac和bc表示数据时钟clk的二分频输出和二分频反相输出,引脚c0和c2表示数据时钟ac的二分频输出和二分频反相输出,引脚c1和c3表示数据时钟bc的二分频输出和二分频反相输出,c0、c1、c2和c3组成四相载波。引脚p1和p2表示输入信码数据data在时钟的作用下串并转换后的输出。引脚cx和cy表示信码数据串并转换后,在同步时钟的作用下差分编码后的输出,引脚qdpsk表示输入的信码数据在同步时钟的作用下四相差分移相键控信号输出。

图3所示电路器件均可从MAX+PLUSⅡ器件库中调用。其中二分频电路涮用1个D触发器和1个非门组成;串并转换电路调用4个D触发器组成;差分编码电路调用2个二异或门、2个D触发器、4个2与门、2个或非门和2个非门组成:四相选相电路调用1个74153组成。调制电路在MAX+PLUSⅡ平台上编译、仿真通过后,打包产生qdpskb组件。

2.2 QDPSK解调电路

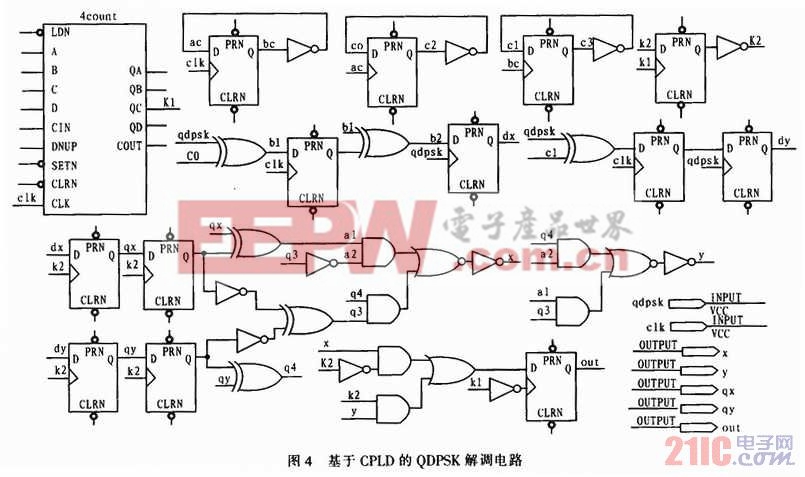

基于CPLD设计的QDPSK解调电路如图4所示。

图4所示QDPSK解调电路引脚关系为:引脚clk表示恢复的数据时钟,引脚k1表示数据时钟clk经过计数器4count的八分频输出,引脚k2表示数据时钟k1的二分频输出,引脚ac和bc表示数据时钟clk的二分频输出和二分频反相输出,引脚c0和c2表示数据时钟ac的二分频输出和二分频反相输出,引脚c1和c3表示数据时钟bc的二分频输出和二分频反相输出,c0、c1、c2和c3组成四相载波。引脚qdpsk表示四相差分移相键控信号输入,引脚qx和qy表示四相差分移相键控信号的相干解调输出。引脚x和y表示相干解调输出在同步时钟的作用下差分译码后的输出,引脚out表示信码差分译码后经并串转换恢复的信码数据输出。

电路器件从MAX+PLUSⅡ器件库中调用。其中二分频电路调用1个D触发器和1个非门组成;相干解调电路调用3个异或门、6个D触发器组成;差分译码电路调用2个D触发器、3个异或门、5个非门、4个与门和2个或非门组成;并串转换电路调用2个非门、2个与门、1个或门和1个D触发器组成。解调电路在MAX+PLUSⅡ平台上编译、仿真通过后,打包产生qdpsky组件。

评论