一类序列信号检测器的设计

2 将触发器接成移位寄存器进行设计

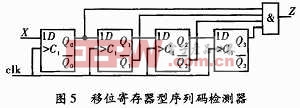

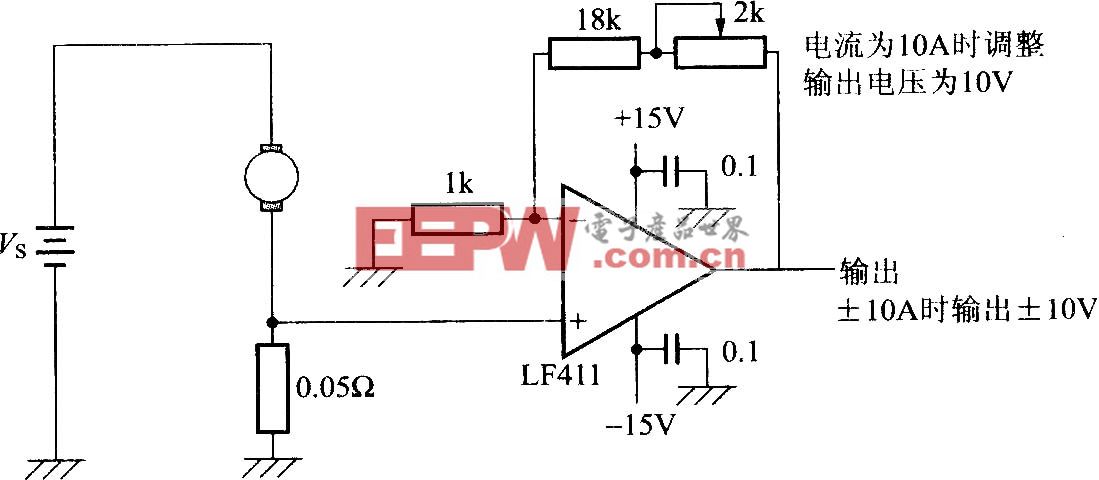

以上设计方法主要依靠电路的状态转换实现序列码检测,虽然所得电路简单,但是设计过程较复杂,特别是当需要检测的序列码位数较长时,工作量较大。为此,将触发器接成移位寄存器的方式,可简化电路设计,同时也便于扩展成位数更多的序列码检测器。用4个D触发器接成的向右移位寄存器。电路如图5所示。

由图5可知,![]() 。在移位脉冲clk作用下,输入端X输入的二进制码依次向右移动,每当出现一个完整的1001序列时,输出端Z便出现高电平。这样就实现了序列码检测的功能。

。在移位脉冲clk作用下,输入端X输入的二进制码依次向右移动,每当出现一个完整的1001序列时,输出端Z便出现高电平。这样就实现了序列码检测的功能。

3 用中规模集成电路进行设计

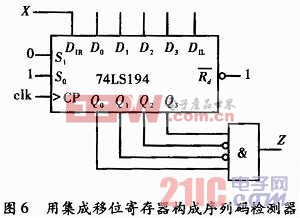

既然用移位寄存器可以实现序列信号检测,那么用集成移位寄存器加少量门电路同样可以实现,而且电路可靠性更高。用4位集成移位寄存器74LS194,实现的序列1001检测器,如图6所示。

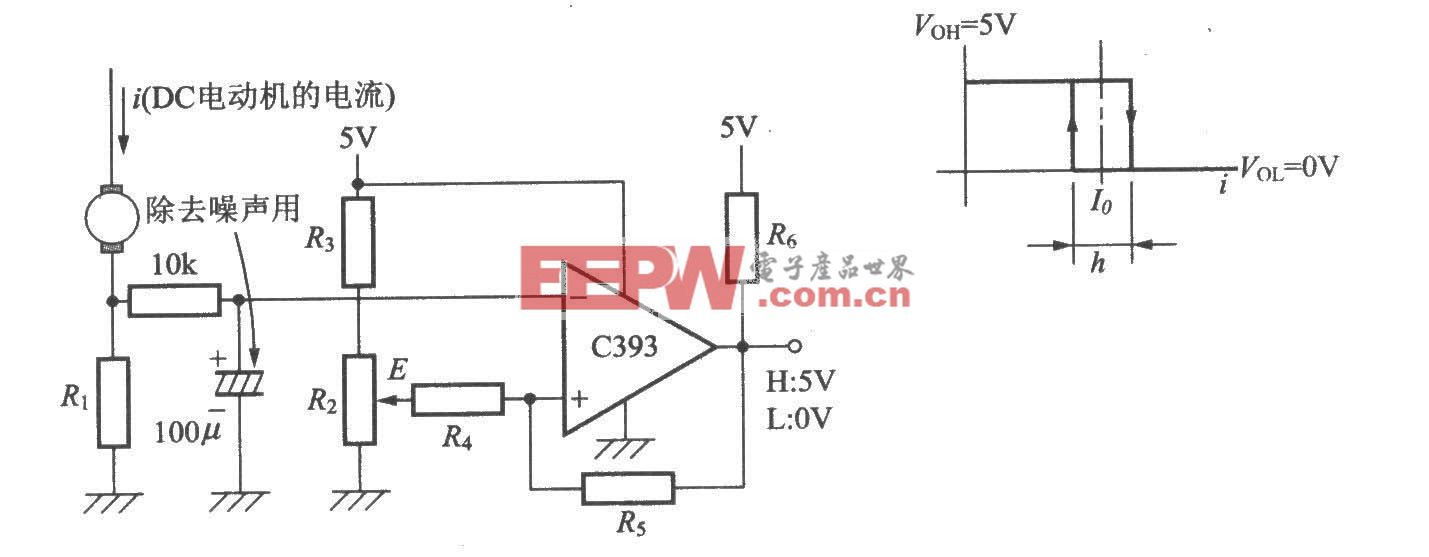

4 当序列不可重叠时的电路设计

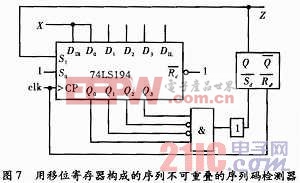

用以上3种方法设计出的电路,都是可序列重叠的序列码检测器,若要求被检测的序列不可重叠,则在方法1中,只需要根据实际情况修改状态转换表即可.后面的设计原理及步骤不变。这种设计方法存在的问题仍然是当待检测的序列位数较长时,设计工作量大、电路可靠性降低。在采用第2、第3种方法设计时,需增加部分控制电路,为保证输入与时钟的同步性,需要使得每当检测出一个序列时,直接将序列的下一位置入寄存器最低位,同时置寄存器其余各位为序列码最后一位的反码以消除重叠代码的影响。此外再用一个锁存器使输出高电平多保持0.5个时钟周期,其优点是:可以消除移位过程中的竞争冒险,使得输出波形更稳定、电路可靠性更高,电路如图7所示。

评论