数字控制DC/DC变换器中ADC的设计

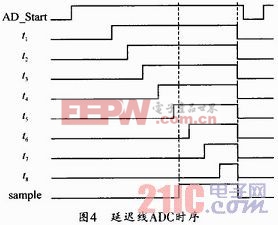

给定一个开始信号AD_Stan,经一定时间间隔后产生一个采样脉冲信号sample,作为D触发器的控制信号。在采样信号有效时对D触发器的输入信号进行锁存,将D触发器的输出信号送至译码电路得到最后的误差信号。图4是延迟线ADC的时序图,假设图2中n=8。在采样信号有效时,AD_Start信号正好传到第5个延迟单元,于是q1~q5输出为1,q6~q8输出为0。采样电压越大,延迟时间td越小,信号传播得越快,输出的温度计码中的1的个数越多。译码电路再将温度计码转换为所需要的二进制码。延迟线ADC即通过输入电源对延迟链供电,根据延迟链延迟时间的大小来确定输入的大小。

3 差分延迟线ADC

3.1 差分延迟线ADC结构分析

延迟线ADC结构简单,功耗小,但易受工艺和温度环境影响,且采样信号需外部产生,增加了电路的复杂性,而且采样信号的延迟大小会影响ADC量化电平的大小,使得系统输出不易稳定。

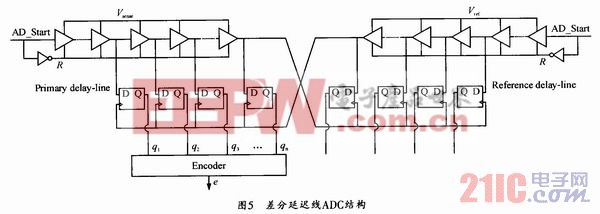

差分延迟线结构是对延迟线结构的一种改进,结构图如图5所示。差分延迟线ADC由两条全同的延迟链组成,主延迟链(Primary delay-line)和参考延迟链(Reference delay-line)。参考延迟链可经主延迟链复制而来。两条差分延迟链共用一个启动信号AD_Start,使两条延迟链的工作状态完全相同。差分延迟链的两个输入分别是采样电压Vsense和基准。

电压Vref,Vsense须小于Vref,根据电压越大延迟越小的原理,参考延迟链先于主延迟链传播完,将与主延迟链相连的D触发器打开,对主延迟链上的Vsense进行采样。这样就实现了将采样电压与基准电压作比较,再通过译码电路得到系统需要的数字误差信号。

差分延迟线ADC的控制信号在内部产生,进一步简化了电路结构。采用差分形式输入,使得采样电压和基准电压同时受到温度和工艺偏差的影响,减少主延迟链的延时偏差。

p2p机相关文章:p2p原理

评论