电荷泵锁相环的数字锁定检测电路应用分析

在数字锁定检测电路设计中,必须严格确保锁定时的相位误差Δt 小于锁定检测窗口TLock_Window,

否则数字锁定指示信号就将出现误判现象。根据前面分析得知,在CDCE72010 锁相环电路中,外部

VCXO 的输入阻抗是数字锁定电路设计的一个关键参数,根据式(2),可以得到压控振荡器输入阻抗的指标要求:

![]()

假设在应用中CDCE72010 中鉴相频率为1MHz,电荷泵电流为1,预设的锁定检测窗口为5.8ns,本

地VCXO 的压控电压为1.65V,则可以得到VCXO 的输入阻抗要求:

![]()

在锁相环电路设计中,鉴相频率和电荷泵电流与环路直流增益成正比,跟锁相环的环路带宽和相位裕量密切相关,为了得到较小的环路带宽,通常需要降低鉴相频率或电荷泵电流。进一步分析式(2),相位误差跟鉴相频率和电荷泵电流成反比,因此在低环路带宽电路的设计中,必须特别注意压控振荡器的输入阻抗(或漏电流指标)和锁定检测窗口的设计,严格满足式(3)的设计要求。

可以通过实验来检查式(3)的正确性。在CDCE72010 的评估板上,改变VCXO 压控端的等效输入阻抗,通过观察CDCE72010 锁定指示输出管脚或锁定指示寄存器的锁定状态,分析该锁定检测电路是否可靠地工作,具体实验设置如下:

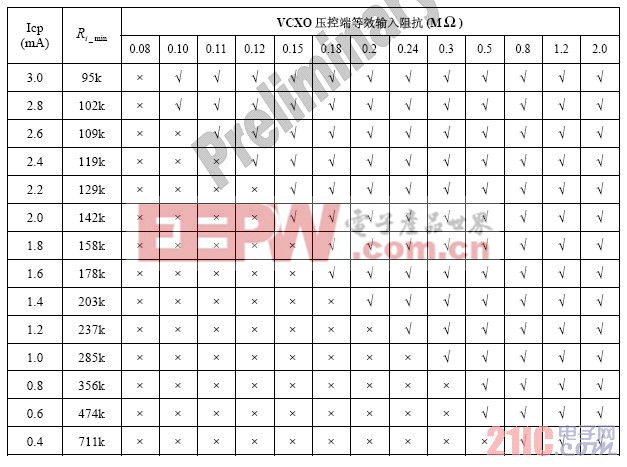

参考时钟为25MHz,VCXO 频率为125MHz,鉴相频率为1MHz,PFD 的检测窗口为5.8ns,控制电

压为1.65V,实验结果如表1 所示,其中R i _ min为计算出的VCXO 输入阻抗的最小值,√表示锁相环指示锁定,×表示锁相环数字锁定指示为失锁状态。其中,在实验过程中,由示波器监控CDCE72010 的参考时钟和本振时钟一直处于锁定状态。

表1 不同VCXO 输入阻抗值对CDCE72010 数字锁定指示的影响

从表1 中可以看出VCXO 的输入阻抗对锁相环的数字锁定有很大的影响,例如当电荷泵电流为1.2mA 时,根据式(3)可以得到VCXO 的最小输入阻抗为237Kohms,那么对于低于这个值的输入阻抗,数字锁相指示无法正确指示锁定,实验测试的结果与理论分析是吻合的。

4 总结

本文在电荷泵锁相环数字锁定检测工作原理的基础上,分析了影响锁定时相位误差的环路参数和外围元器件的关键参数,包括电荷泵电流、鉴相频率和漏电流等。同时根据对整个环路漏电流路径的分析,重点分析了外部压控振荡器的等效输入阻抗对锁相环锁定指示准确性的影响。

以CDCE72010 数字锁定设计为例,为了提高数字锁定检测电路锁定状态指示的准确性,在低环路带宽的锁相环电路设计中,必须选择恰当的外部压控振荡器的输入阻抗参数指标。

DIY机械键盘相关社区:机械键盘DIY

低通滤波器相关文章:低通滤波器原理

电荷放大器相关文章:电荷放大器原理 电流传感器相关文章:电流传感器原理 鉴相器相关文章:鉴相器原理 数字滤波器相关文章:数字滤波器原理 锁相环相关文章:锁相环原理 锁相放大器相关文章:锁相放大器原理

评论