一种新型高线性度采样开关的设计

2 应用Flip-around采样保持电路验证

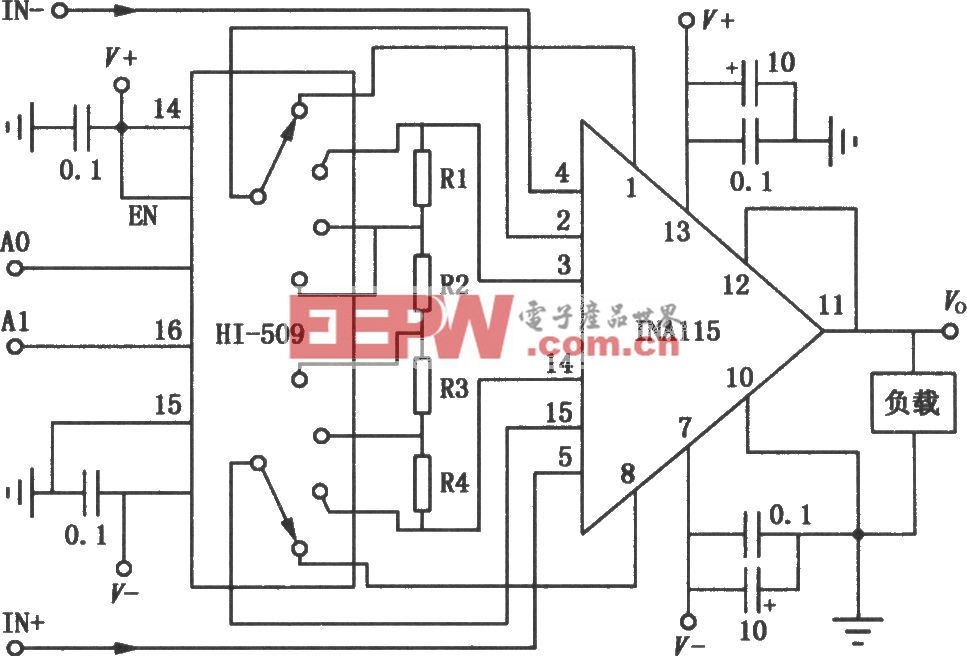

电容翻转型(Flip-around)采样保持电路由于反馈系数β较大,等效到输出的噪声也相应减小,同时与传统的电荷传输型采样保持电路相比,其功耗更低。因此采用此结构对新型开关进行验证。

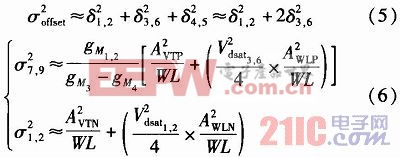

图5是采用电容翻转型采样保持电路的结构。为有效地抑制直流偏置和衬底噪声,同时减小偶次谐波失真,提高线性度,采用全差分输入输出结构;又由于CMOS开关固有的非理想效应,如沟道电荷注入以及栅极时钟馈通等,这会造成输入与输出之间的误差,需采用下级板采样技术克服。为与普通CMOS对管开关对比,进行2次FFT仿真,其中图5中的输入开关S0分别采用两种不同的采样开关,即普通的CMOS对管开关和本文设计的采样开关。两种情况下其他开关均使用普通单管开关。本文引用地址:http://www.eepw.com.cn/article/178157.htm

采用华虹NEC 0.18 μm MMCMOS工艺,电源电压1.8 V,运用Cadence Spectre软件以及Matlab对电路进行了仿真和FFT性能分析。图5所示为采样保持电路采样率为100 MHz,输入信号为47.94 MHz正弦波时的无杂散动态范围(Spurious Free Dynamic Range,SFDR)FFT分析如图7所示,其SFDR为91 dB。同理仿真得到同等条件下采用普通CMOS对管开关的采样保持电路,其SFDR如图6所示为72dB,通过对比,本文设计的采样开关较普通CMOS开关的采样保持电路的SFDR性能优异,从而实现了设计目标。

3 结束语

设计了一种新型的采样开关,与传统CMOS对管开关相比,其具有更好的线性度,可应用在ADC的采样保持等电路中,以使整个系统达到更好的SFDR。

评论