实现数字电源转换的方法

降压式转换器的输入与输出电压的关系可以表示为:

VOUT = VIN (D,其中D = PWM占空比= TON/(TON + TOFF)

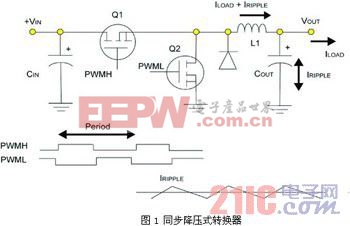

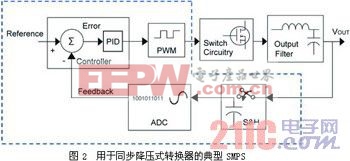

一个降压式转换器理想的输出电压是输入电压与晶体管占空比的乘积。通过检测(见图1),如果晶体管Q1是常通的,输出电压将等于输入电压。如果Q1是常断的,那么输出电压将为零。实际上,当负载电流增加时,晶体管和电感器两端存在的电压降将会增加。图2给出了如何使用DSC设计数字SMPS控制系统。

采样保持(S/H)电路通常每2~10ms进行一次采样,ADC需要大约500ns将模拟反馈信号转换成为数字值。PID控制器是一种运行于DSC的程序,有大约1~2ms的计算延迟。该控制器输出可以转换为一个PWM信号,由它来驱动开关电路。当进入新的占空比时,如果PWM发生器不能立即更新其输出,就可能出现明显的延迟。晶体管驱动器和相关的晶体管也会引入大约50ns到1微秒的延迟,其长短因使用的器件和电路设计而异。

2 计算控制环路的延迟

总控制环路延迟是ADC采样与转换时间(500ns)、PID计算时间(1μs)、PWM输出延迟(0)、晶体管切换时间(50ns)和PID执行速度时期(2μs)之和。这个例子中的总环路延迟是3.65μs,这意味着最大有效控制环路的采样率为274kHz。虽然尼奎斯特定理需要2倍的采样率来重建一个信号,数字控制环路仍必须以6倍至10倍采样率进行采样。这样做的原因是只使用2倍的采样率,相位滞后将180度。利用2倍采样率,我们已经用完了180度的相位滞后“预算”,而没有考虑系统中任何其他的延迟。一个采用8倍采样率的系统单在采样过程引入45度的相位滞后,这是一个好得多的采样率。为了有足够的相位容限,许多数字控制系统对模拟信号进行了10倍或更高的过采样。假定最高有效采样率为274kHz,有效控制带宽是其八分之一,也就是大约34kHz。

3 SMPS设计中PWM的重要性

不同的电源规范推动着对不同电源拓扑结构的需求,这些不同的拓扑结构需要不同的PWM模式,其中每一种都支持多种SMPS设计,包括标准、互补、推挽、多相位、可变相位、电流复位和电流限制PWM模式。最基本的PWM模式是标准的边沿对齐式PWM,其中的导通与关断时间之比控制着电源电流。每对输出中只有一个PWM输出被用于这些异步降压式、升压式和反激式转换器电路。同步降压式转换器采用互补PWM模式,其中的互补输出控制一个由MOSFET实现的 “同步开关”整流器,而不是通常的整流器。互补PWM模式还可以用于采用同步整流来改善系统效率的其他电路。

推挽式转换器通常用于DC/DC转换器和AC/DC电源。“多相PWM”术语描述的是多PWM输出而不是边沿对齐的。多相转换器电路经常用于必须提供大电流、负载变化可能非常迅速的应用的DC/DC转换器。由于PC电源的广泛使用,相位变换PWM模式正变得越来越常见。Microchip的dsPIC DSC SMPS系列可以支持当前广泛用于电源行业的所有已知的PWM模式。

评论