基于集成计数器的N进制计数器设计与仿真

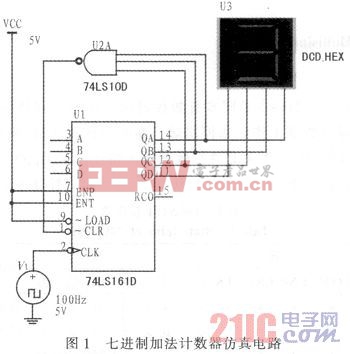

如图1所示电路是基于集成4位二进制同步加法计数器74LS161,用归零法设计的七进制加法计数器的仿真电路。由于74LS161的清零端为异步控制方式,则最大计数状态SN=S7=0111;由此求出归零逻辑

用归零法设计N进制计数器要注意以下两点:

1)当集成计数器的清零端为同步控制方式,则不会出现过渡状态SN,此时最大计数状态应为SN-1,相应归零逻辑也由SN-1求得。

2)若MN,需要用多个M进制集成计数级联,扩展成大容量计数器后,再使用归零法设计N进制计数器。

2 三十六进制加法计数器的设计与仿真

2.1 基于74LS161的三十六进制加法计数器的设计与仿真

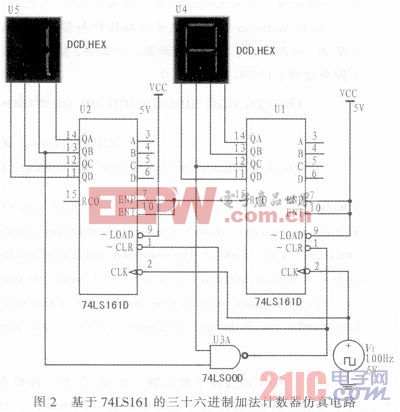

74LS161为十六进制计数器,设计三十六进制计数器需要两个74LS161通过级联的方法,可先扩展成256(16×16)进制计数器。设低位的74LS161编号为1,高位的74LS161编号为2,再用归零法设计如下:

1)写出SN的二进制代码:SN=S36=100100;

2)求出归零逻辑:![]() ;

;

3)在仿真平台Multisim中选择2个74LS161,1个74LS00,2个5 V电源和地,根据归零逻辑创建仿真电路;

4)时钟电压源V1接入计数脉冲输入端CLK,用带译码的十六进制数码管U4和U5作状态输出的显示器,完整的三十六进制计数器仿真电路如图2所示。

评论