基于FPGA和DDS的数控信号源的设计与实现

2.3 地址信号发生器的设计

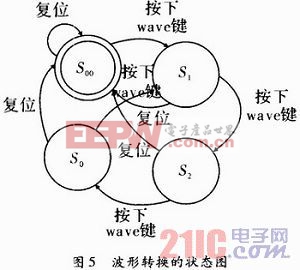

考虑到ROM的结构和每周期采样点数相同的需要,设计的地址信号发生器需要在提供ROM寻址的同时完成波形选择的功能。当波形选择键“wave”按下时,完成波形种类选择功能。波形种类转换采样状态机来完成,其状态图如图5所示。图中共有4种状态S00,S0,S1,S2。当复位信号有效时为S00状态,此时输出正弦波,否则每当按下“wave”键就从当前状态转换到下一状态。状态S0输出正弦波,状态S1输出方波,状态S2输出三角波。当“wave”键没有按下,且相位累加器溢出时,地址信号发生器就是一个N进制的计数器,使ROM表顺序地读出当前波形数据。本文引用地址:http://www.eepw.com.cn/article/177446.htm

2.4 外围电路的实现

外围电路包括幅度控制、显示以及输入模块等部分。

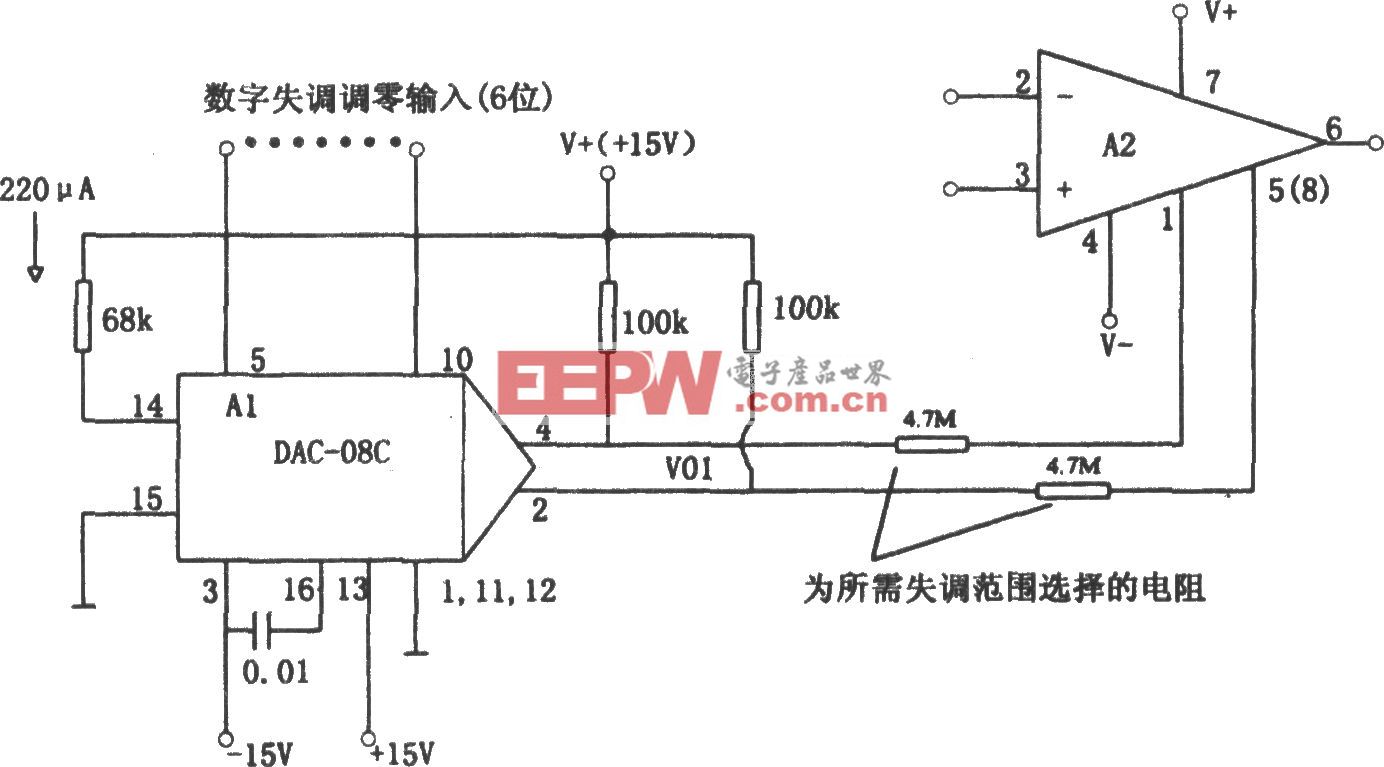

幅度控制通过调节比例放大电路来实现。显示模块由LED数码管和指示灯组成,其中8位数码显示频率,指示灯显示波形种类。用动态扫描方式依次点亮8位数码管。

输入模块用于输出波形选择和波形频率设置,均由4×4键盘完成。波形选择只用一个按键完成,按下后循环选择“正弦波→方波→三角波→正弦波”,同时输出相应波形种类指示灯信号。

根据系统中DDS结构,输出波形的频率为

![]()

式(1)中,fclk为系统时钟频率;Fword为频率控制字;Mode为相位累计器的模,N为每种波形数据的字长。由于fclk,Mode,N均为定值,所以输出频率与相位控制是比例关系,可用一个乘法器来实现。文中取fclk=50 MHz,Mode=5×107,N=32,则f0=Fword/32,输出波形频率精度为0.03 Hz。根据采样定理,输出频率f0最高为fclk的1/2,但是实际上f0低于fclk的40%时,输出波形的稳定性才比较好。

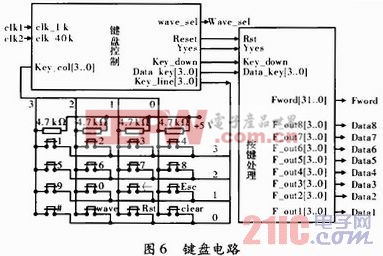

键盘电路如图6所示,由键盘、键盘控制和按键处理3部分组成。键盘控制完成键扫、按键去抖和按键标志产生功能。按键处理部分对数字键和功能键的处理。频率设置时,输入的数字作为波形的输出频率,并转换成对应的频率控制字送入DDS模块。设置频率的同时,输入的设置值送入显示模块显示。

按键说明:“←”键表示删除最后一位输入的数字,“esc”键表示放弃当前输入的数字,“#”键表示确定输入,“wave”键表示波形种类选择,“reset”键为复位键,“clear”键为清零键。输出频率设置操作为从键盘输入需要输出的频率值,最后按下确认键“#”即可。

评论