基于FPGA和DDS的数控信号源的设计与实现

2 电路设计与实现

系统中循环相位累加器、ROM表和地址信号发生器是关键部分,它们直接决定系统性能。

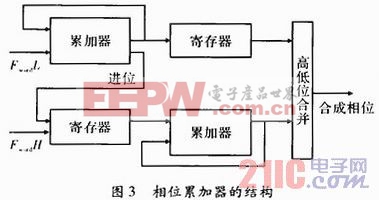

2.1 相位累加器结构设计

为得到足够高的分辨率,文中循环相位累加器字长取32位。但是,若直接采用32位串行加法器作为累加器,则引入的延迟较大,从而大大降低系统的工作速度。为此,文中采用超前进位原理和流水线技术设计32位循环累加器,其原理框图如图3所示。每4位超前进位加法器作为一个基本单元,4个4位超前进位加法器组成16超前进位加法器,并且将入流水技术加入16位超前进位加法器中。最后再将两个16位加法器组成32位加法器,如图3所示。本文引用地址:http://www.eepw.com.cn/article/177446.htm

2.2 ROM查找表设计

理论上,一个周期内样点数越多,输出的波形精度越高。但样点数越多,需要的存储空间也越多。为了得到一定精度的波形,又不希望大幅度地增加存储容量,人们提出如下方法:(1)利用CORDIC及其改进算法来设计DDS。(2)根据抽样定理,存储最少的样点数,每个周期采用固定的样点数。(3)利用波形的对称性来减少ROM,如正弦波只需存储前1/4周期的波形数据。

ROM查找表设计的标目是减少ROM的容量,同时不能过多增加系统的复杂度。根据采样定理,每个波形周期只需采样45°,135°,225°,315°相位点对应的4个样值,就可以无失真地重构模拟波形信号。为保证波形质量,文中每个周期固定采样32个点,则3种波形有96个样点,每个样点用8为二进制数表示,则共需要768 bit。因此,地址信号发生器可设计为32进制的计数器。

ROM查找表结构如图4所示,其中头N个样值为正弦波数据,最后N个样值为三角波数据,中间是方波数据。若要输出正弦波,则从第1个存储单元开始查找;要输出方波,则从第N+1个单元开始查找,依次类推,图中N取32。

传统DDS技术中随着波形频率的增加,采样点数明显减少,使得波形质量也大大降低。采用这种方法,不管输出波形多大,采样点数都是固定的,从而避免以上问题。

评论