基于65nm工艺数字IC物理设计中信号串扰的预防

摘要:数字集成电路的不断发展和制造工艺的不断进步,使得物理设计面临着越来越多的挑战。特征尺寸的减小,使得后端设计过程中解决信号完整性问题是越来越重要。互连线间的串扰就是其中的一个,所以在后端设计的流程中,对串扰的预防作用也显得尤为重要。本文就TSMC 65nm工艺下,根据具体的设计模块,探索物理设计流程中如何才能更好的预防串扰对芯片时序的影响。

关键词:串扰;物理设计;数字集成电路

0 引言

近年来,随着我国集成电路设计水平和工艺技术的提高,芯片的集成度持续提高到了惊人的地步,电源电压逐步降低以及时钟频率不断提高,在芯片功能越来越强大的同时,也意味着所有与信号完整性SI(signal integrity)相关的问题都变得越来越严重。集成电路技术的发展使得在后端物理设计过程中电路布线的复杂性不断增加,庞大又复杂的设计中电路门数的剧增使更多、更长的金属互连线成为必要,导致了布线层数的不断增加,同时相邻的沟道电容也在增大,所以在深亚微米及以下工艺的IC后端设计流程中,有效地预防串扰的影响也变得越来越重要。

1 基于IC Compiler的物理设计过程中对串扰的预防措施

在物理设计过程中,串扰的预防可以有很多方面,下面主要讨论后端设计阶段的标准单元布局、时钟布线和总体布线相应对串扰的预防措施。

在标准单元的布局阶段,可以通过设置一些约束来控制工具自动化布局,从而改善后面串扰的影响。最主要的方法有对标准单元的拥塞度和连线的跳变时间的控制。对于跳变时间的约束,我们可以在后端设计的流程中控制max_transition值;对于拥塞的改善,在IC Compiler的布局阶段,可以让工具ICCompiler增加拥塞驱动来进行自动的标准单元布局的工作,具体实现是在place_opt后面增加选项-congestion。

在时钟树的布线阶段目前最主要的方法是将时钟连线的宽度和间距加倍(dsdw)的布线规则和对时钟连线采用屏蔽(shield)的布线规则。在ICCompiler中用define_routing_rule来实现。

在全局布线阶段,IC Compiler在自动布线中就有串扰这一选项;将该选项打开,工具在布线的时候就会考虑串扰,并尽可能将其修复,即route_opt-xtalk_reduction。为了更好的作用,需要在布线之前将信号完整性分析打开:set_si_options-delta_delay true-route_xta lk_preventation_thresholdvalue,该阈值大小的设置也很重要。

2 对串扰预防的各种方法的实践及比较

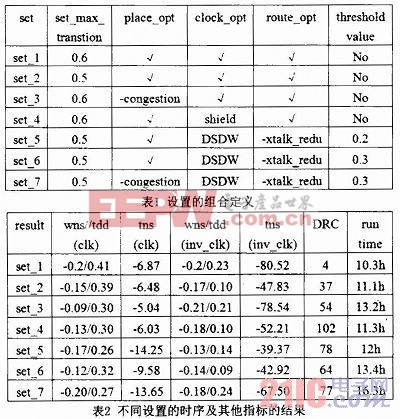

有理论基础和对IC Compiler的掌握后,下面就利用可重构芯片项目中一个100多万门的模块core_1作为实践目标,探索预防串扰方法的较理想的流程。该设计采用的工艺是TSMC 65nm工艺,在core_1的设计中有半周期的时序路径,这部分的路径上时序是比较紧张的,将其归为inv_clk的组,另外的寄存器之间的时序路径就归为clk的组。如下表1、2所示,给出的是各种实验数据。表1为表示各种不同设置的表格,该表格给出的是设置的不同处,流程中没写出来的其他的设置均是相同的。表2就是根据表1中的不同在core_1中所得到的实验结果,表2中的tdd表示该数据路径上串扰引起的总的附加延迟(Totaldelta delay)。

对于表1,“√”表示的是该步骤最基本的流程,而“-congestion”是表示在place_opt后面增加选项-congestion,“DSDW”表示在时钟树综合流程中采用的是双倍线宽和间接的规则, “shield”表示在时钟树综合流程中采用的是屏蔽的时钟树布线,而threshold value栏中的“No”表示布线时串扰选项没有打开,0.2/0.3就是打开SI的选项-routextalk_preventation_threshold的值。

表2是表示在表1中的不同设置的流程下,core_1的实际结果wns//tdd表示的是最差路径时序违规和该路径上总的串扰产生的延迟,tns是总的时序违规,clk和inv_clk是指core_1里不同的路径组(pathgroup)。其中inv_clk是半周期的路径,其时序相对比较紧张。

由表2的实验结果可知:对传输时间的约束不仅改善串扰的作用,还对整个时序都有比较好的提高,并得知在TSMC 65nm工艺下,将最大的传输时间约束在0.5ns是比较理想的;布局阶段的拥塞驱动可以很好地改善串扰的延迟,并对时序比较宽松的路径时序也得到很好的改善,但是对于时序紧张的路径其影响是不利的;时钟树阶段对时钟布线采用DSDW和shield的规则对时序的优化和串扰延迟的抑制起到了很好的效果;在自动布线阶段打开工具对串扰的减少这一功用,对时序和串扰延迟均是有好处的,其阈值对于TSMC 65nm的工艺设置为0.3更为合理。而set_5、set_6、set_7说明了在整个后端流程中set_6的设置对于core_1这个设计来说是最合理的,因为其不仅预防了串扰延迟也很好地兼顾了clk和inv_clk两个group的时序。

3 结论

在65nm及以下的数字芯片的物理设计过程中对串扰的预防是很重要的,现通过对core_1芯片的实践,我们可以看出,对于时序比较好满足的情况下,设置最大传输时间的约束、在拥塞驱动下进行标准单元布局、采用dwds规则的时钟布线、采用设置合适的阈值下的减少串扰作用的自动布线程序,这样的流程对于串扰的预防是有效的。而对于时序不好满足的情况下设置最大传输时间的约束;在时序驱动下进行标准单元的布局;采用dwds规则的时钟布线;采用设置合适的阈值下的减少串扰作用的自动布线程序,这样的流程更为理想。

评论