CMOS工艺多功能数字芯片的输出缓冲电路设计

1.2 缺点

上述设计规则仅仅是从速度优化方面考虑。在驱动很大的负载电容时,为了减小延迟时间,缓冲器中反相器的级数就越多,这将使总面积很大,而且也将增大缓冲器的功耗。在实际设计中应在满足设计速度的前提下,尽量减少反相器链的级数,适当增大比例因子S,这样可以使总面积和总功耗减少。

很多情况下往往对最终输出级的上升、下降时间有一定的要求。在这种情况下应根据给定的上升、下降时间要求和实际负载电容,设计出最终输出级反相器的尺寸,再综合考虑速度,面积和功耗等因素设计缓冲器的前几级电路。

2 不同的输出缓冲器设计方案的比较

在一款多功能数字芯片的设计时考虑到芯片的驱动能力和所采用的0.6μm的CMOS工艺,最终级反向器的尺寸为:PMOS管为W=540 μm,L=0.6 μm,NMOS管为W=216μm,L=0.6μm。第一级为芯片内部电路尺寸,PMOS管为W=20μm,L=0.6μm,NMOS管为W=8μm,L=0.6μm。由以上分析可以知道,当输出反向器链采用不同的级数时,芯片的上升时间、下降时间和延迟时间是不同的,而且采用不同的级数时芯片所占用的面积也是不同的,下边我们通过三种不同的反相器链设计方式来对比,从中选出最合适的输出缓冲器链的设计方式。则输出缓冲器器链的设计为:

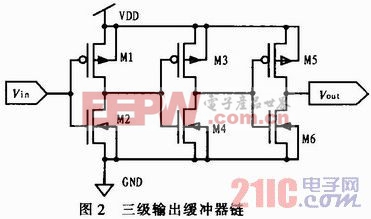

1)把输出缓冲器设计为第一种三级反相器链,如图2所示。本文引用地址:http://www.eepw.com.cn/article/176990.htm

M5 pmos 1=0.6μm w=180μm M6 nmos 1=0.6μm w=72 μm

M3 pmos 1=0.6 μm w=60 μm M4 nmos 1=0.6μm w=24μm

M1 pmos 1=0.6μm w=20μm M2 nmos 1=0.6μm w=8 μm

通过HSPICE仿真软件,在0.6μm CSMC 2P2M CMOS工艺库下的仿真结果(负载为100 pF电容,1 kΩ电阻)如图3(a)(b)(c)(d)所示。主要考虑仿真结果中的输出反向器链的上升时间tr、下降时间tf、上升延迟和下降延迟td。

评论