基于Multisim的VHDL建模与仿真

1.2 基于Multisire的VHDL建模

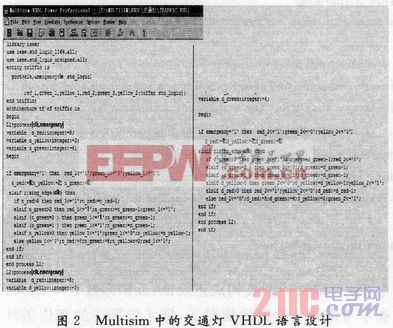

(1)Multisim中的VHDL语言编辑

由于Multisim软件不能直接使用VHDL模块,需要同时安装Multisim 2001软件。

①用Multisim中的VHDL-SIMULATION模块完成VHDL语言的编辑,命名为“traffic.acc”。

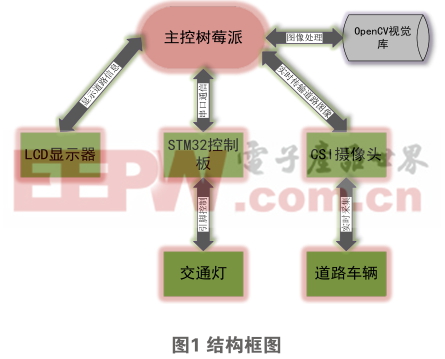

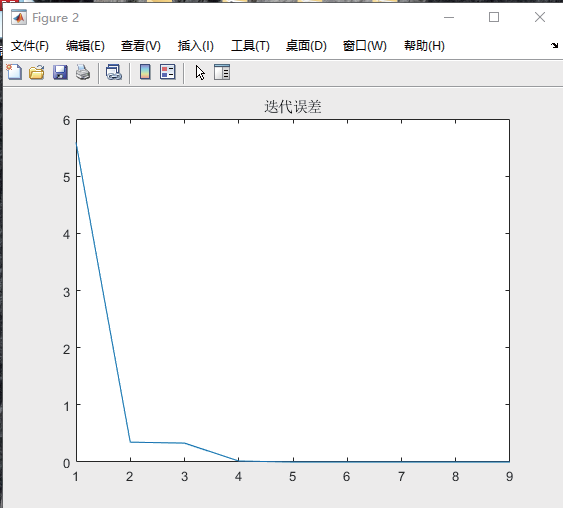

②编译链接编辑好的VHDL语言,除了检查VHDL语言错误外,编译链接会产生一个“*.vx”文件,只有这个文件才能在制作元件封装时调用,见图2。本文引用地址:http://www.eepw.com.cn/article/176079.htm

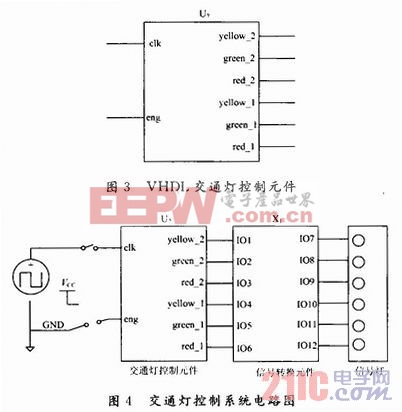

(2)Multisim中元件制作封装

Multisim使用模块化的仿真方法,VHDL语言不能直接在Multisim软件中仿真。在Multisim中使用COMPONENT WIZARD命令进行交通灯的元件封装制作。

①点击TOOL中的COMPONENT WIZARD命令,输入元件名字和元件类型,还可以输入作者名字。

②输入元件引脚数和元件引脚参数设计。包括引脚名称,该名称必须和VHDL语言中的名字相同;引脚类型,输入或输出等类型;元件外形的制作。

③仿真模型选择。输入模型名字,添加生成的VHDL语言文件“*.vx”。

④制作封装好的交通灯元件如图3所示。

2 基于Multisim的VHDL仿真

设计中的CLK信号采用Multisim元件库提供的时钟元件。交通信号灯采用Multisim元件库提供的traffic_light元件。

电路如图4所示。

由于交通灯控制元件U7的输出高电平有效,而元件库提供的traffic_light元件是低电平有效,在电路中设计子电路模块XI实现高低电平的转换。

从图4和图5的仿真可知,基于Multisim的VHDL电路能够实现设计的要求,并且利用这种方法电路设计模块化,既可以有传统的波形仿真也可以有直观的实物验证效果。对于复杂的电路可以将其划分为小的子模块在Multisim中进行VHDL设计,然后将子模块进行连接达到电路设计的要求。

3 结语

本文通过将Multisim与VHDL相结合,实现了简易交通灯控制系统的电路设计,通过仿真验证了这种方法的有效性。这种方法还可以解决EDA教学过程中没有FPGA开发板或者实验设备缺乏的情况下如何利用虚拟仿真软件仿真。

评论