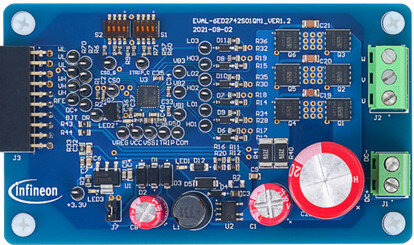

具有自适应开机和冬眠功能的电源管理设计

3.1 功能框图和信号、构件说明

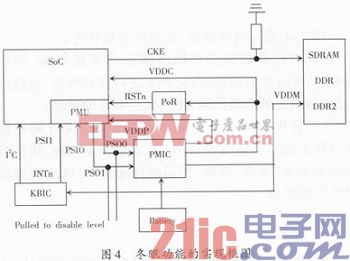

冬眠功能的实现框如图4所示。本文引用地址:http://www.eepw.com.cn/article/175786.htm

图4中的部件:SoC为主控芯片;PMU为主控芯片内的电源管理单元;PMIC为电源管理芯片;SDRAM为动态存储器,包括DDR/DDR2/DDR3等;PoR为复位发生器;KBIC为键盘控制芯片,用于唤醒“冬眠”,其INTn与PSI1相连,I2C连到SoC的相应接口;KBIC由VDDM供电;图4中的信号:VDDP/VDDM/VDDC为PMIC的电源输出,分别给PMU,SDRAM/KBIC和其他部分供电;CKE是从SoC输出至SDRAM的控制信号,用于控制SDRA M的自刷新状态;SoC的电源使能输出PSO0/PSO1被拉到关断状态(如果使能电平为高,拉到GNDP,否则拉到VDDP)。

3.2 冬眠功能实现过程

3.2.1 进入冬眠

(1)软件保存快速启动代码和当前程序现场到SDRAM;

(2)软件控制SDRAM进入自刷新模式(CKE=0并保持到唤醒之后);

(3)软件控制SoC预备进入“冬眠”模式(包括停时钟,关PLL等);

(4)软件将快速启动的初始地址写入PSR;

(5)软件将2’bI0写入PCR(即关VDDC,保持VDDM);

(6)硬件上PSO0输出高阻,PSO1输出有效使能电平;由于VDDC掉电,RSTn拉低复位有效;CKE输出为高阻,由下拉保持在低电平使SDRAM维持自刷新状态。

3.2.2 唤醒冬眠

(1)用户按下指定键导致PSI1拉低达到阈值时间,触发冬眠唤醒逻辑;

(2)硬件控制PSO0输出有效使能电平使VDDC上电;

(3)SoC进入复位阶段,其中CKE的复位值为0;

(4)PoR在经过固定延迟后太高RSTn,使复位失效;

(5)SoC进入启动阶段,控制权交给软件;

(6)软件判断此为冬眠唤醒而非开机启动,控制SDRAM跳出自刷新状态;读PSR获得启动地址,直接运行SDRAM上的启动代码,并回到冬眠前的现场;

(7)软件判断引起冬眠唤醒的原因,执行相应操作。(在上述功能框图中,KBIC被用作唤醒部件,按任意键都会引发“冬眠”唤醒,然后软件通过I2C读出键值确定所按何键)。

4 结语

自适应开机功能简化了PCB上供电电路的设计,也使系统设计者能自由选择性价比更高的PMIC从而有助于降低整机成本;自适应开机的实现方法已由笔者所在公司申请专利保护。

本文所公开的冬眠功能已成功用于电纸书的应用:读者阅读当前页时,SoC进入冬眠状态,超级省电;当读者按动翻页键(PgDn或PgUp)时,SoC快速复活并显示下一页或上一页的内容,然后又开始冬眠。当使用Mobile SDRAM作为外部动态存储器时,笔者测量其电纸书参考系统的普通待机功耗为2.2 mA,而在“冬眠”状态下的待机功耗为180μA(主要来自Mobile SDRAM的自刷新功耗)。由是,利用冬眠功能本电纸书一次充电后的使用时间可从数周延长到数月。

评论