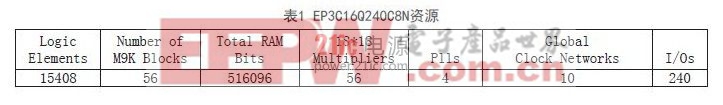

基于FPGA的SOPC系统DAB发射端硬件实现

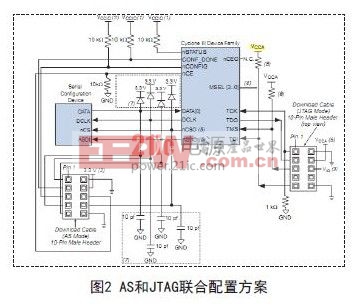

2.1 配置电路

FPGA芯片按配置速度快慢依次为:

Active parallel(AP)模式.Fast passiveparallel(FPP)模式.Active serial(AS)模式.Passive serial(PS)模式.另外还有用于调试的Joint Test Action Group(JTAG)模式.本文FPGA同时配置AS模式和JTAG模式.

根据cycloneIII的数据手册,配置方案由MSEL引脚决定.当使用AS和JTAG两种方式时,MSEL[3:0]为“010”.如图2所示为ATERA给出的AS和JTAG配置电路.

AS模式是指FPGA的EPCS控制器发出读取数据的信号,从而把串行FLASH(EPCS系列芯片)的数据读入FPGA中,实现对FPGA的编程.配置数据通过FPGA的DATA0引脚送入,数据被同步在DCLK输入上,1个时钟周期传送1位数据.本文中选取的配置芯片EPCS16SI8,有16Mbits的存储空间,可以支持DCLK时钟工作在20MHz和40MHz.

JTAG接口是一个业界标准接口,主要用于芯片测试等功能.ALTERA的FPGA基本上都可以支持JTAG命令来配置FPGA的方式,而且JTAG配置方式比其他任何方式优先级都高.JTAG模式是将配置数据存储在SRAM,掉电后需重新下载.它与FPGA的接口有4个必需的信号TDI,TDO,TMS和TCK以及1个可选信号TRST构成.

2.2 外部存储器电路

SDRAM比FLASH速度快,比SRAM存储空间大,在FPGA系统中一般把SDRAM作为NIOS处理器的RAM和程序运行空间.本文中选择IS42S16100-7T这款SDRAM作为FPGA的外部存储器.IS42S16100-7T的信号电压为3.3V,有16Mbits的存储空间,最大速度可达到143MHz.在SOPC Builder里根据时序参数表设置SDRAM控制器.

锁相环相关文章:锁相环原理

评论