TMS320VC5402 DSP的并行I/O引导装载方法研究

在上述程序中,END标号给出I/O读入操作结束后所转移的入口地址,之后转到61H和62H给出的入口地址执行用户程序。第1~4行读入入口地址;第5?|8行读入数据块长度;第9~13行读入数据块首地址;第14~20行读入数据块。为了更好地了解这段程序的工作过程及其原理,图2给出了8位并行I/O Bootloader程序流程图。第21~34行为读数据子程序,在该程序中,利用了XF和BIO信号与外部I/O进行握手联络,其信号时序如图3所示。

本文引用地址:http://www.eepw.com.cn/article/173788.htm

本文引用地址:http://www.eepw.com.cn/article/173788.htm3 C5402并行I/O引导装载方法的实现

3.1 硬件电路分析

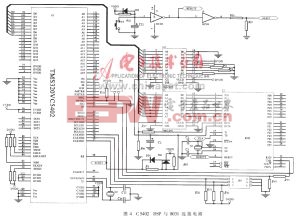

为了满足C5402 DSP 8位并行I/O Bootloader引导程序的时序要求,本文利用8031单片机作智能I/O部件,图4为C5402与8031的连接电路图。在图中,U3为TMS320VC5402DSP,U?为8031单片机,U1、U2均为SN74AHC245,单片机系统中的EPROM电路没有给出。

U1、U2的DIR引脚接地,数据传输方向为B→A。U2的B7~B4和B2~B0接地,B3接DVDD(3.3V),/CE端接系统复位信号,保证了在上电复位期间U2给C5402提供00001000B数据,使其进入8位并行I/O引导模式,而当复位信号无效后,U2的/CE=“1”片选信号无效而脱离系统。U1的作用是数据缓冲兼作电平转换器,U1的VCCD端接4.3V,其作用是将8031输出的TTL电平转换成5402能接受的CMOS电平;U1的/CE断接8031的P3.3(/INT)脚,在系统复位直到执行CLR P3.3之前都保持高电平,在此期间U1无效,保证了U2正常供给5402所需的数据。8031的P3.0(RXD)、P3.1(TXD)作为握手信号,分别与C5402的/BIO和XF相连。JP3、JP4可供用户跳线选择C5402的系统时钟以及选择C5402的运行模式。

3.2 程序设计

根据以上分析,本文设计了如下8031汇编程序。首先使U1的/CE有效,然后等待C5402的XF为低电平,XF=“0”后,使8031的P3.1=“0”即BIO=“0”C5402进入等待数据状态。在数据送到数据总线之后,使BIO=“1”通知C5402读取I/O端口数据。程序中,UC定义的代码前面22个字节是与C5402的联络码,从第23个字节开始才是用户程序代码。

・

・

・

CLR P3.3 ;使U1(AHC245)CE=0

W1: JB P3.0、W1 ;XF=1等待

CLR P3.1 ;使BIO=0

MOV R4、#00H ;初始化变址寄存器

W2: JNB P3.0、W2 ;XF=0等待

MOV DPTR、#UC ;指向用户代码首地址

MOV A、R4 ;变址送A

MOVC A、@A+DPTR ;取用户代码

MOV P1、A ;送到数据总线

SETB P3.1 ;使BIO=1

W3: JB P3.0、W3 ;XF=1等待

CLR P3.1 ;使BIO=0

INC R4 ;指向下一代码

CJNE R4、#0FFH、W2 ;未完重来

UC: DB 08H、0AAH、00H、00H

DB 00H、00H、00H、00H

DB 00H、80H、00H、25H

DB 00H、00H、00H、80H

DB 0F4H、95H、0E9H、27H

DB 0F3H、10H ;以上为与C5402的联络码用户程序代码

TMS320VC5402 DSP是C54X家族乃至TI的DSP家族的最新成员,正以其极高的性价比被越来越多的用户所接受。本文利用廉价、通用的8031单片机实现C5402 8位并行I/O Bootloader功能,一方面,可以很好地解决快速DSP与慢速I/O(EPROM)之间的数据传输问题;另一方面,C5402 Bootloader成功后,8031还可作为“协助理器”使用,从而极大提高了系统的灵活性和实用性。具有广阔的应用前景。

评论