基于单片机和FPGA的频率特性测试仪的设计

2.4 相位测量模块的方案

该模块采用相位一时间转化法。两个频率相同、相位不同的正弦信号经整形异或运算后产生脉宽为Tx、周期为T的方波,相位差与(TX/T)之间始终存在一一对应关系。因此无论频率如何变化,只要测出(Tx/T),相位差的大小也就确定。本文引用地址:http://www.eepw.com.cn/article/173597.htm

3 理论分析与计算

3.1 DDS相关计算

由DDS原理可得:

式中,N为相位累加器位数,K为频率控制字。

当K=1时,可知DDS的最低输出频率为:

此即DDS的频率分辨率。

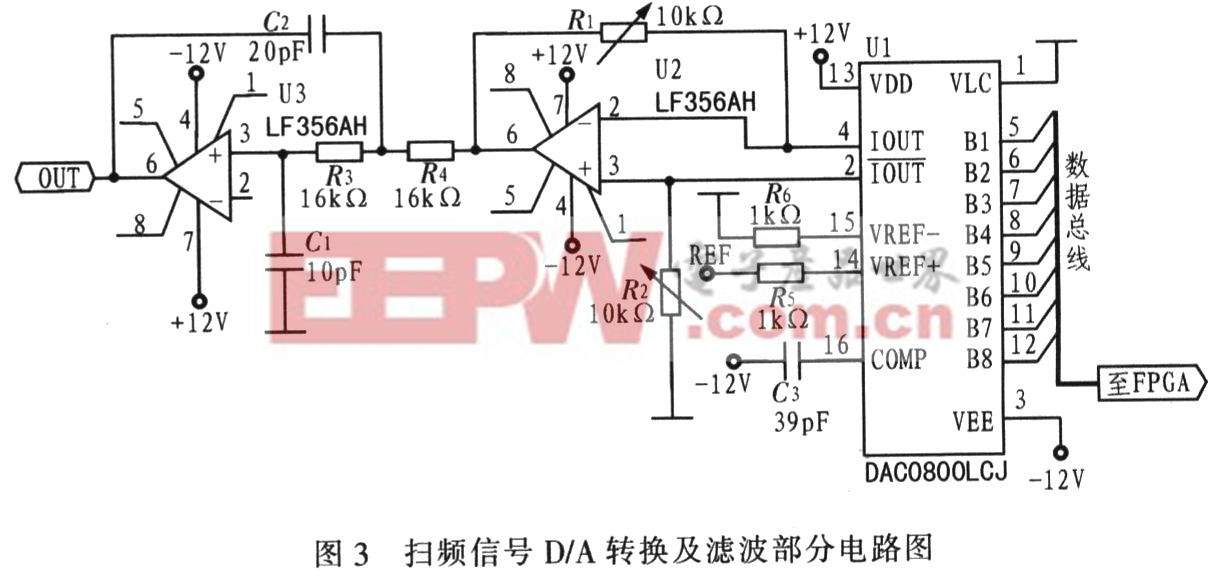

(1)移相信号发生器部分DDS由于输出级D/A转换器DAC0800的建立时间为100 ns,则时钟频率应小于10 MHz,取时钟频率fout=8.388 608 MHz,相位累加器N=23bit,则:

(2)扫频信号部分DDS 由于FPGA片内资源丰富,为保证足够的扫频精度,取参考时钟频率fclk为40 MHz。通过控制频率控制字K的变化范围,完全可以满足DAC0800的速度要求。

3.2 相位测量相关计算

由FPGA利用等精度法测得被测信号和基准时钟的频率分别为f0、fCP,对被测信号鉴相后,由得到的相位差脉冲宽度T控制计数器计数,其计数值设为M,则被测信号的相位差为:

(1)相位测量误差计算 若让计数器在1 s内累计记数,则累计数:M1=Mf0,式(5)改为

![]()

其测量误差△φ为:

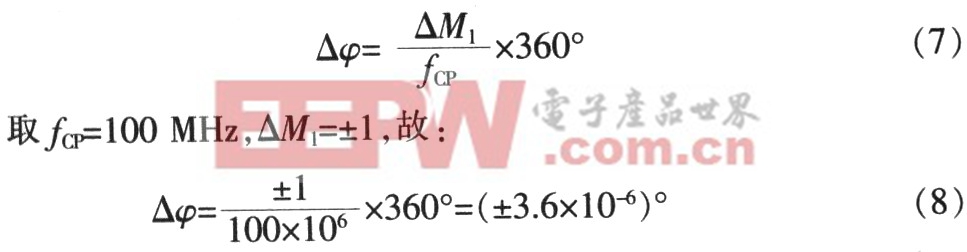

(2)相位测量分辨率计算 数字移相信号发生器频率范围为20 Hz~20 kHz,相位差测量范围为0~359°,因此计数器时钟频率fclk至少为72 MHz,取fCP=100 MHz,由于计数器分辨率为±1,对应最小相位分辨率(f0=20 kHz时):

4 系统整体框图

系统设计发挥FPGA稳定、可靠、可编程的特点,让FP-GA实现尽可能多的功能,从而减少模拟部分的工作,使整个设计更加可靠。系统整体框图如图2所示。

评论