51单片机串口通讯设计

输出输入接口的扩展 本文引用地址:http://www.eepw.com.cn/article/173406.htm

单片机串口实现并行通信,其原理就是将PC机传过来的并行数据转换成串行数据,送入单片机的串口再由其进行相应处理。实质上就是一个数据串-并、并-串转换的过程。

PC的并口为一个标准的25针插座,包含一个八位二进制数据端口(地址为378H),即第2脚到第9脚;一个输入控制端口(地址为379H),即第15脚、13脚、12脚、10脚、11脚,其另外低三位无定义;一个输出控制口(地址为37AH),即第1脚、14脚、16脚、17脚,其另外高四位无定义。由此可见后面两个端口都不是完全的8位。

输出接口电路扩展

这里使用常用的移位寄存器74LS164与单片机的RXD口构成输出接口电路。

双列直插式74LS164引脚定义如图1所示。

其中:QA~QH为并行输出的数据,送入PC机并口378H端口(接收数据的8个数据位);单片机串口输出的数据从AB输入;CLR信号用于清除输出数据(通常用在移位完成时);内部数据移位依靠时钟CLK信号上升沿(由单片机TX提供)控制。

表1是该芯片工作的真值表。

输入接口电路扩展

使用常用的移位寄存器74LS165与单片机的RXD口构成输入接口电路。

双列直插式74LS165引脚定义如图2所示。

其中:A~H为并行输入的数据,接PC机并口378H端口(接收数据的8个数据位);单片机串口接收的数据(RXD端口)从QH输入;SH/LD信号用于重新装载数据(通常用在数据完全移出后);SER是用于填充数据移出后的空位的逻辑电平信号(逻辑1或0);而数据是否移动由CLK INH和CLK联合控制;内部数据移位依靠时钟CLK信号(仍由单片机的TXD提供)上升沿控制。

表2是该芯片工作的真值表。

其他软硬件准备工作

输入输出控制端口的连接。将单片机的P3.4、P3.5口分别与PC并口的第15脚、第16脚相连。这样在进行数据通信时,两者的握手信号传输就解决了:当并口的第16脚置高电平时,用来通知单片机接收PC机已准备就绪的数据,单片机收到以后就可以进行相应控制,接收数据;当单片机接收完数据时,会置P3.4为高电平并被379H的第15脚接收,于是PC机准备发送下一个数据……单片机向PC机发送数据时,情况与此类似,由P3.4发送信号给PC机,而由P3.5接收PC机发送过来的信号。

软件方面,由于是用串口进行并行通信,因此就不能将串口的工作方式设置为方式0(移位寄存器输入/输出方式)以外的其他方式。还要注意此时串口的波特率固定为单片机外接晶振频率的1/12。串行数据通过RXD输入/输出,TXD用于发送控制输入输出数据移位的时钟脉冲。收发的数据为8位,低位在前。

设计实例

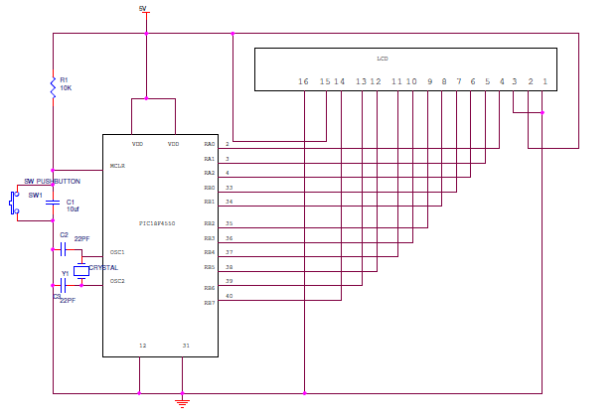

由于这一并行通信实现方法非常简单,所以对于有一定单片机编程经验的开发人员来说,只要硬件电路确定下来,软件方面的问题就非常容易。图3为电路原理图。

需要说明的是:1、单片机与PC机并口要共地;2、由于并行通信存在应答信号(本图中由单片机的P3.4、P3.5实现此功能),所以不会出现RXD端口数据混乱的情况。

小结

现在单片机的应用越来越广泛,单片机与PC之间的通信是一个非常重要的应用。如果单纯的从实现单片机与PC的并行通信的角度来说,该实现方法并不是最简单的。最简单的方法是将PC的并口对应引脚与单片机的P1口和P3口直接相连,然后软件上实现。本文的目的是充分利用单片机的串口资源与PC机进行通信。

评论