基于单片机的等效采样示波器设计

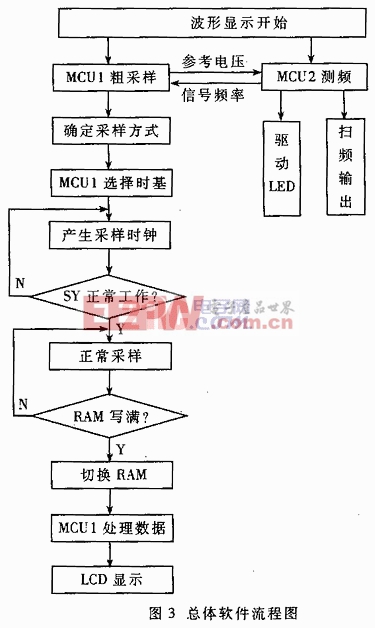

(1)控制器 控制器部分任务较重,通过两片89C52(MCU1和MCU2)来完成。其中,MCU1负责采样、数据处理以及程序时钟和液晶的控制工作;MCU2完成测频、DAC输出和键盘接口处理功能。两单片机通过串口通信。

(2)测频模块 本系统输入信号的频率范围较宽(1Hz~80MHz),隔度范围较大(0.1V~2.2V),整形电路采用高速比较器TL3016实现,其参考电压由MCU1对输入信号采样获得。整形后的信号经程控分频器送至MCU2测频,精度可达四位有效数字。

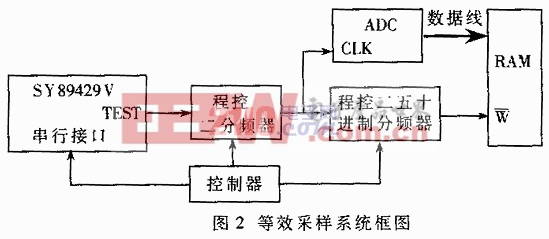

(3)波形采样模块 该模块由40MSPS的模数转换器TLC5540、静态存储器CY7C128A-20和可编程逻辑器件ispLSI1016E-80组成。 在程控时钟和程控分频器的控制下,CLPD产生存储器地址,将高速ADC的采样数据以程控频率写入静态RAM。写满256个点后,将静态RAM的控制权通过数据选择器转交给MCU1,由MCU1进行数据处理,并送液晶显示。 (4)程控时钟电路 程控时钟电路是本系统实现等效采样的关键,其核心是可编程频率合成芯片SY89429V。SY89429V的输出时钟范围是25MHz~400MHz,步进值0.125MHz~1MHz。它内部采用高频锁相环结构,对干扰很敏感,在硬件上采取了一定的抗干扰措施保证其稳定工作。 (5)液晶显示 液晶部分由点阵液晶显示器EDM160160、液晶控制器SED1335、SRAMHM62256、负压发生器和背光交流驱动电路发生器组成。 2.2 等效采样的实现 等效采样是本系统的关键和创新点。主要采用以芯片SY89429V为核心的精密时钟发生电路,控制高速ADC对高频信号进行循环间歇式采样。 实现等效采样的系统框图如图2所示。

等效采样的输入频率是1.25MHz~80MHz。为了使复现的波形尽量精确,系统设计在1.25MHz~40MHz信号范围内每周期采一样一个点,在40MHz~80MHz信号范围内每个周期采一个点来复现波形。即采样频率范围要在1MHz~40MHz之间,并有可控的小步进值。 SY89429V的输出频率为25MHz~400MHz,需要外加分频电路将低低频部分扩展。同时,本系统选用的ADC为TLC5540,其转换速率是5MSPS~40MSPS,低端采样率会受到限制,可以采用控制RAM写入速度的方式来控制采样速率。综合考虑,采用CPLD器件,将SY89429V芯片TEST输出的FOUT频率经过程控二分频器,一方面提供给ADC作为CLK工作频率,另一方面再经过程控二五十进制分频器控制RAM写入速度,作为低端信号的采样频率。

评论