基于S3C2410A设计的工程地震仪方案

3.2 硬件介绍

3.2.1 协处理器模块

系统的协处理器采用Xilinx公司的FPGA,型号为SPARTANIIE XC2SIOOE。该芯片共有2700个逻辑单元,10万个逻辑门,片内块RAM为40KB。其具体实现以下功能:

· A/D模块读/写时序控制;

· 生成FIFO,其主要功能是存储经A/D编码的数据:

· 提供ARM处理器控制信号。

FPGA芯片分4部分来实现上述功能:

(1)内部控制信号产生器

FPGA对50 MHz时钟分频产生A/D芯片采样时钟Sampleclk和ARM处理器外部时钟Sysclk;Sysclk经锁相环电路(PLL)后产生ARM处理器工作所需的时钟信号 。

(2)ARM控制器

提供ARM处理器正常工作所必须的各种控制信号;实现ARM处理器地址总线、数据总线和外部中断信号接入 。

(3)A/D控制器

控制A/D模块的数据转换。产生A/D转换起始信号(/HOLD),检测数据转换完成信号(/EOC),产生FIFO写入信号,实现数据转换通道选择。

(4)FIFO存储器

生成FIFO,完成A/D转换数据的存储。

3.2.2 ARM处理器模块

ARM 处理器模块由FLASH、SDRAM 和s3C2410共同构建。系统选用Samsung公司的K9F1208UOA构建8位FLASH 存储器系统。K9F1208UOA单片容量为64 MB;选用两片单片容量32 MB。数据宽度为16位HY57V561620CT,并联构建32位SDRAM存储器系统,共64 MB的SDRAM空问可以满足嵌入式操作系统和各种复杂算法的运行要求。ARM处理器对各模块的控制则是通过底层驱动控制协处理器FPGA产生各种控制信号来实现。

3.2.3 预处理和A/D模块

传感器传播的模拟信号比较微弱,需要经过前置放大等预处理后方具备数据有效性。预处理主要是由前置放大电路构成,A/D模块主要由模拟开关和A/D转换芯片构成。模拟开关采用AD公司的AD7506,可实现12通道数据采集。A/D转换芯片采用CIRRUS公司的CS5381,是120dB、192kHz高性能立体声24位Σ 一△ A/D变换器,内置双极性电路构成的混合集成转换显片,具有外接元件少,功耗低,精度高等特点,并且具有自动校零和自动极性转换功能,只需外接少量的阻容件即可构成一个完整的A/D转换器。

3.2.4 接口和显示模块

包括常用的接口和显示器件。接口包括常用的串口等,用以进行数据的外部存储。显示模块主要包括构成操作的LCD和触摸屏等外围显示设备。

4 嵌入式系统软件设计

软件部分分为FPGA控制程序和ARM处理器两部分,FPGA用VHDL来设计,基于s3C2410A的软件设计主要任务有数据采集的驱动程序,操作系统的移植以及上层应用软件的设计。嵌入式操作系统应用WinCe.net,上层应用软件开发使用Em-bedded Visual C++,底层驱动和ARM处理器的调试则使用c语言。

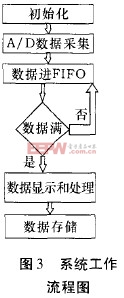

系统开始工作后ARM处理器和FPGA协处理器中的FIFO开始初始化。经A/D转换后的数据存入对应的FIFO中。FIFO中的数据容量达到一定限度即产生巾断,ARM处理器中的主程序产生中断等待线程;一旦中断产生则进入中断服务程序,读取数据,之后进入ARM系统进行相应的处理,然后存储到存储设备。如图3所示。

评论