一种应用于ARM7的CMOS图像采集系统

Samsung公司的S3C4510B是基于以太网系统高性价比的16/32位RISC微控制器,内含一个由ARM公司设计的16/32位 ARM7TDMI RISC处理器核,ARM7TDMI为低功耗、高性能的16/32核,它具有0.9MIPS/MHz的三级流水线结构,支持32位ARM指令集和16位 Thumb指令集,有着功能丰富的片内外围功能模块,可挂载大容量的存储器,最适合用于对价格及功耗敏感的应用场合。 CMOS(Complementary Metal Oxide Semiconfuctor),即“互补金属氧化物半导体”。它是计算机系统内一种重要的芯片,将它加工也可以作为图像采集系统中的感光传感器。随着 CMOS技术的发展及市场需求的增加,这种图像传感器得以迅速发展,它具有高度集成化、低成本、低功耗、单一工作电压、局部像素可编程、随机读取等优点,适用于超微型数码相机、摄像机、安防监控、汽车防盗、机器视觉、指纹识别、手机等图像领域。本文介绍的是由美国OmniVision公司生产的 OV7640彩色CMOS图像传感器,它采用独特的传感器专利工艺技术和先进的算法(algorithms)解决了先前CMOS感光器件固定图像噪声(FPN)的限制。由这两种芯片组成的系统有较强的实际应用价值。

本文引用地址:http://www.eepw.com.cn/article/171431.htm1 系统的基本硬件组成

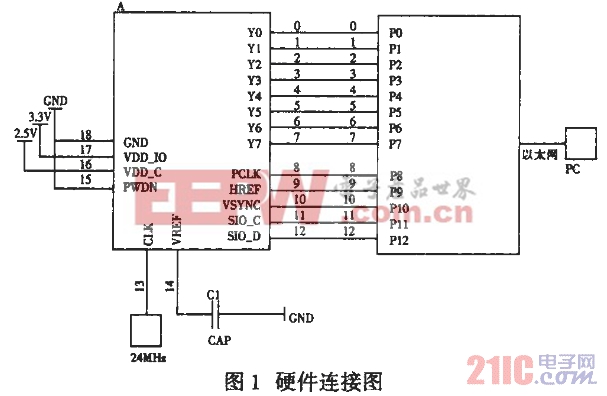

整个图像采集系统主要有CMOS图像传感芯片OV7640、三星4510B控制器(板载64M存储器)、晶振电路、电源几部分组成。

OV7640是高度集成的彩色摄像芯片,可带1/4”镜头,支持多种格式,内设的SCCB(Serial Camera Control Bus)串行控制总线接口,提供简单控制方式,通过该接口,我们可以对OV7640芯片内部所有寄存器值进行修改,从而完成对OV7640的控制。另外,OV7640内置了640×480分辨率的镜像阵列,A/D转换器,并支持外部水平、垂直同步输入格式,外部微控制器和RAM界面、数字视频输出、增益控制、黑白平和白平衡等在内的控制寄存器功能模块。

S3C4510B是一款不带MMU的ARM7微处理器,可在其上运行uCLinux操作系统。它的系统时钟最高可达60MHz,有着丰富的外部资源接口,系统板载了64M的存储器,可直接利用板载的存储器进行图像数据的暂存,以最大限度的简化系统。

系统的时钟频率由一颗24MHz的有源晶振提供,系统电源为5V,S3C4510B需要1.8V和3.3V的电压,OV7640需要2.5V和3.3V的电压输入,可通过电平转换芯片LM1117进行转换得到所需要的电压。

2 硬件设计的思路和要点

系统功能是应用4510B芯片的GPIO口对OV7640图像数据进行采集,然后进行相应的处理和识别。OV7640包含有8位数据D0-D7、同步信号VSYNC、HREF、PCLK,这些信号需要送给CPU以读取图像数据和保证同步;另一方面,由于OV7640默认帧频为30Hz,在此帧频下的图像数据输出为30Hz*307.2K=9.216Mbytes/s,QVGA方式的数据率为30Hz*76.8K=2.3Mbytes/s,在不考虑同步的情况下已远远超过I/O口的响应速度,因此必须重新设置以降低帧频。因此,在本系统中对OV7640的访问有三个:第一是设置地址号为0x11的帧频控制器CLKRC以降低帧频,第二是设置地址号为0x14的控制器COMC以设置像素为320*240,最后是设置地址号为0x28的COMH以设置扫描格式。从信号的使用角度来说,需要用到OV7640的8位数据线D0-D7(双向),同步信号VSYNC、HREF、PCLK(单向,供控制器读),SCCB总线SIO_C(单向)、SIO_D(双向)。

由于4510B板上IO口资源相当丰富,8位并行数据线和控制线都可以接在IO口上,设置好输入输出关系,通过软件模拟SCCB总线实现控制器对 OV7640的控制。连接采用4510为主机,OV7640为从机的方式。在设置完帧频以后就可以根据同步信号对一帧一帧的图像进行采集了。系统连接图如图1所示。

3 图像采集的工作过程

1)通过SCCB总线设置OV7640的帧频

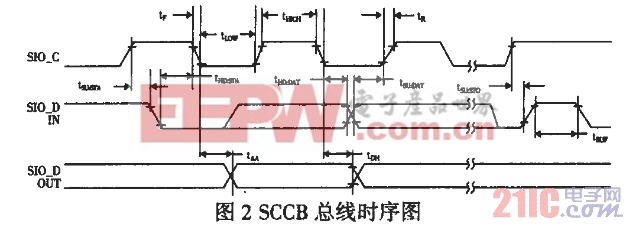

系统上电后需要对CMOS图像传感器进行初始化,以确定采集图像的开窗位置、开窗大小和黑白工作模式等。这些参数是受OV7640内部相应寄存器的值控制的,可通过SCCB总线对其进行设置。SCCB的接口有SCCE、SIO_C、SIO_D(SCCE是串行总线使能信号,SIO_C是串行总线时钟信号,SIO_D是串行总线数据信号)三条引脚。OV7640芯片上没有SCCE引脚,但也可实现单主对单从方式的通讯,控制总线规定的条件如下:当 SIO_C为高电平时,如SIO_D产生一个下降沿表明数据传输的开始,如SIO_D产生一个上升沿表明数据传输的结束;为了避免传送无用的信息位,分别在传输开始之前、传输结束之后将SIO_D设置为高电平。在数据传输期间,SIO_D上数据的传输受SIO_C的控制,当SIO_C为低电平时,SIO_D上数据有效,SIO_D为稳定数据状态,SIO_C每出现一正脉冲,将传送一位数据。其中两根线的上升和下降时延、高低电平的维持时间都有较严格的要求,软件的延时时间要根据CPU速度和GPIO口的速度精确的计算后才能使通讯保持顺畅。如图2所示:

评论