与MCS51系列单片机相同的数据存储器扩展技术解析方案

1.3.2 逻辑段表设计与段的存取管理

为了便于对段的存取管理控制,设计一个逻辑段表,表的内容为逻辑段号。因为1个逻辑段为64KB,它与2个物理段(每段32KB)相对应,因而逻辑段表示的长度为实际物理段总数的一半。设有N个段,逻辑段表如图3所示。例如:有8个32KB的物理段,逻辑段表的长度为4B,逻辑段表的内容为:0,1,2, 3。实际的物理段号为:0,1,2,3,4,5,6,7。每个逻辑段号与2个物理段号相对应。

另外,为了便于存取控制,设计一个将逻辑地址自动转换成物理地址的子程序,子程序必须简单。经过分析,把每个32KB的物理段的起始地址都设为8000H,即每个32KB的物理段的段内地址都是从8000H~0FFFFH。根据逻辑地址与物理地址的对应关系,笔者设计了一个子程序,由于结构简单,只给出具体流程图,如图4所示。子程序的入口参数为逻辑段号与逻辑偏移地址,返回结果为物理段号与物理段内地址。这样,对段的存取访问可先查逻辑段表查出逻辑段号,再调用该子程序实现。

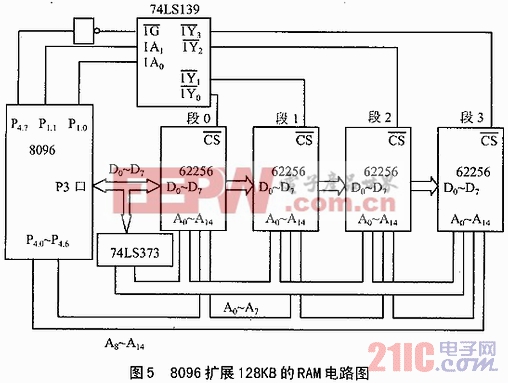

2 设计举例:8096扩展128KB的RAM

分析:由于地址空间为128KB,因此可以设置4个大小同为32KB的段,每段选用1个62256芯片。电路原理分析:8096的P3口输出直接作为数据总线使用,同时外接74LS373的输出,作为低地址总线A0~A7;P4口的P4.0~P4.6作为高地址总线A8~A14使用,P4.7经过一反相器连接74LS139(双2~4译码器)的1G(使能器);P1.1、P1.0分别与74LS139译码器的两个输入端1A1、1A0相接。P1.1、 P1.0、P4.7分别作为高地址总线A17、A16、A15使用。译码器的输出1Y3、1Y2、1Y1、1Y0分别与4个寄存器62256的片选信号 CS相接。这样可以得出:段0存储器的物理地址为08000H~0FFFFH,段1存储器的物理地址为18000H~1FFFFH,段2存储器的物理地址为28000H~2FFFFH,段3存储器的物理地址为38000H~3FFFFH;而逻辑地址为00000H~1FFFFH。逻辑段表的内容为0、1,具体电路如图5所示。

3 总结

这种段式管理的数据存储器扩展技术简单方便,具有很大的优越性,具体体现在以下几方面:从应用角度看,此技术能够实现大容量的数据存储器的扩展,数据存储器可采用RAM、EEPROM、FLASH RAM等;最大的扩展容量为8MB,远远超出了一般应用系统的数据存储器扩展需求。从用户角度看,用户在编程时不必考虑实际物理数据存储器的地址空间是否连续,通过段式管理,使用连续的逻辑地址来编程,克服了不连续物理地址空间的缺陷,而且,对各段存储的数据提供了保护;在一般的大数据量的单路信号检测与处理系统中,此技术使得用户对连接采集数据的存取是透明的,不受硬件的局限,便于用各种高级语言开发设计。从硬件角度看,对于数据存储器采用多个32KB 的RAM芯片,各存储段相互独立,互不影响,各段的存储器芯片的故障也不会对整个系统造成很大影响;在一般的多数大数据量的信号检测与处理系统以及由单片机组成的集散式控制系统中,可以为每路采集的数据分酌情不同的段来存储,这样对各段存储的数据提供了保护,提高了整个系统的可靠性,应用效果是非常理想的。对于数据存储器采用单个大容量的EEROM或FLASH RAM芯片时,硬件电路更为简单,不需要译码器等电路。

评论