基于串口通信的单片机仿真和C语言开发

1)先将数据线置高电平1;2) 延时(该时间要求不是很严格,但是要尽可能短一些);3) 数据线拉到低电平0;4) 延时 750us(该时间范围可以在480~960us);5) 数据线拉到高电平1;6)延时等待。如果初始化成功则在15~60ms内产生一个由DS18B20 返回的低电平0,据该状态可以确定它的存在。但是要注意,不能无限地等待,不然会使程序进入死循环,所以要进行超时判断;7) 若 CPU 读到数据线上的低电平0 后,还要进行延时,其延时时间从发出高电平算起最少要480us;8)将数据线再次拉到高电平后结束。

2. DS18B20 写数据

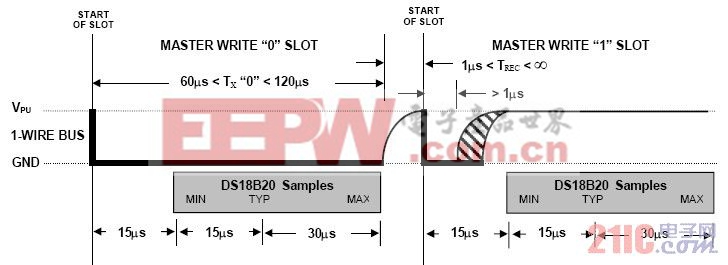

图3.3 写数据时序图

1) 数据线先置低电平0;

2)延时确定的时间为15us;

3) 按从低位到高位的顺序发送数据(一次只发送一位);

4) 延时时间为 45us;

5) 将数据线拉到高电平1;

6) 重复 1)到5)步骤,直到发送完整个字节;

7)最后将数据线拉高到1.

3. DS18B20 读数据

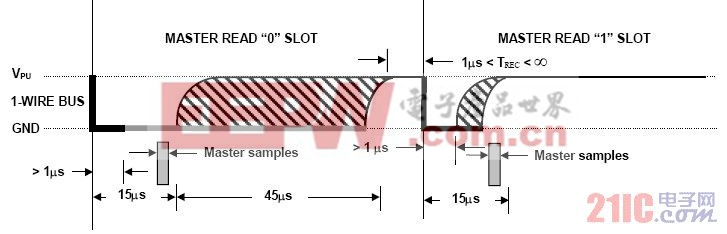

图3.4 读数据时序图

1)将数据线拉高为1;

2) 延时 2us ;

3) 将数据线拉低0 ;

4) 延时 6us ;

5) 将数据线拉高1 ;

6)延时 4us ;

7) 读数据线的状态得到1 个状态位,并且进行数据处理;

8) 延时 30us ;

9) 重复 1)到7)步,知道读取完一个字节。

4 硬件设计

4.1 时钟电路及复位电路

1.时钟电路

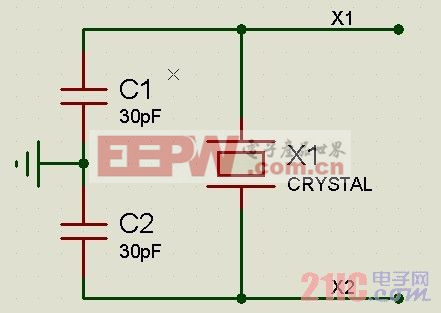

时钟电路可以产生CPU 校准时序,是单片机的控制核心,本次设计是通过外接12MHz的晶振来实现时钟电路的时序控制。在使用片内振荡器时,XTAL1 和XTAL2 分别为反向放大器的输入端和输出端。外接晶体以及电容C3 和C5 构成并联谐振电路,接在放大器的反馈回路中。当用外部时钟驱动时,XTAL2引脚应悬空,而由XTAL1引脚上的信号驱动,外部振荡器通过一个2 分频的触发器而成为内部时钟信号,故对外部信号的占空比没有什么要求,但最小和最大的高电平持续时间和低电平持续时间应符合技术要求。电路如图4.1 所示。

图 4.1 晶振电路

评论