基于单片机的大程序和数掘空间的设计和实现

单片机是一种集成在电路芯片,是采用超大规模集成电路技术把具有数据处理能力的中央处理器CPU随机存储器RAM、只读存储器ROM、多种I/O口和中断系统、定时器/计时器等功能(可能还包括显示驱动电路、脉宽调制电路、模拟多路转换器、A/D转换器等电路)集成到一块硅片上构成的一个小而完善的计算机系统。

本文引用地址:http://www.eepw.com.cn/article/170930.htmMCS51系列单片机是目前应用非常广泛的8位MCU。MCS5l系列单片机的地址总线为16位,不作扩展的情况下其最大的程序和数据地址空间为64 KB。但是随着控制领域的不断智能化、复杂化,程序代码或数据空间的大小可能远远大于64 KB。结合相应的硬件地址扩展,使用KeilC5l的Blank Switch技术可生成代码长度和数据空间大于64 KB的目标程序。

1 Blank Switch技术介绍

具体实现Blank Switch技术的是KeilC5l中的分组连接定位器BL5l。Keil C5l语言源程序经过C5l编译器编译后,生成浮动地址的目标代码文件。这种浮动地址的目标代码必须经过连接定位器BL5l的连接和定位,生成具有绝对地址的目标代码,才能写入程序存储器正常运行。

BL51支持分组连接定位,允许生成代码大于64 KB的目标程序,可以在具有适当硬件扩展逻辑的系统中进行代码组之间的切换,以达到正常运行的目的。

在Keil C5l开发工具的快速更新过程中,LX51成为功能更为完善的连接定位器,使用它替代BL51能够增加更多的连接定位功能。笔者使用LX5l可以更加方便程序的开发。

2 系统硬件的设计

在采用BL5l对目标程序进行分组连接定位时,要求系统具有相应的硬件分组扩展逻辑。BL5l默认的分组方式是采用MCU的P1端口作硬件扩展地址线。采用l条Pl引脚时,分组数为2,采用6条P1引脚时,最多可分为64个代码组,剩余的Pl口线也可做其他用途。

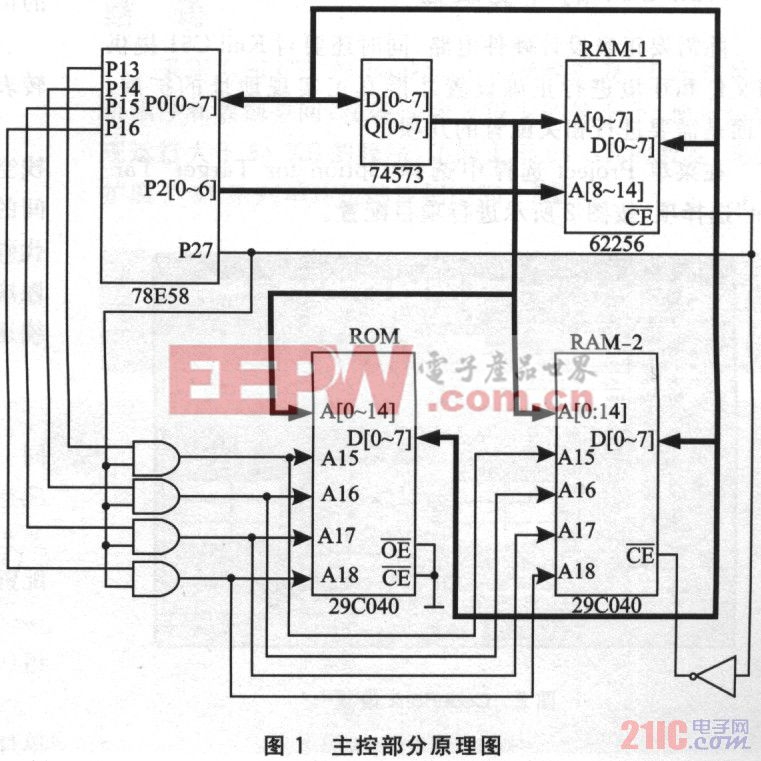

在系统中,以Pl端口作硬件扩展地址线,使用了4条Pl引脚(P1.4~P1.7)。主控部分硬件基本原理图如图1所示。在这里,去除了外围控制接口(如串口)与其他CPU的互联等电路,主要突出如何实现使用Pl端口作硬件扩展来增加程序空间和数据空间。笔者使用Flash29C040作为程序存储器,由于程控交换机中有很多参数和设置数据需要断电保存,所以使用了另一Flash29CO4O作为扩展的外部数据存储器。

在和数据存储器的连接中,增加了P1.O和P2.7组合对数据Flash 29C040的片选,主要是考虑可以增加主控芯片对外围器件的控制。例如,当设置P1.0为0,地址为高32KB时,可以扩展增加访问串口或其他器件。在本文就不再对该部分内容详细描述了。同时,需要注意安排好变量的存储地址,这一点将在下文中详细描述。

在程序设计过程中,P1扩展地址线对程序员而言是不可见的。由BL5l产生的代码来控制硬件的扩展引脚和代码组的切换,这使程序员只需要将精力花费在代码编写和代码组的安排上,大大提高了程序设计效率和稳定性。

评论