基于SoC的MPEG-4视频解码加速器

引言

本文引用地址:http://www.eepw.com.cn/article/170661.htm随着MPEG-4应用的普及, 符合MPEG-4标准的视频在手持设备上的应用越来越广泛, SoC技术可以在完成其它功能的同时, 在手持设备上低成本低功耗的实现MPEG-4视频解码。而基于SoC的解码方案可以有多种, 例如采用CPU 内核软件解码,也可引入DSP核, 或者设计专用的硬件加速电路。但是, 软件解码在系统繁忙时难以满足实时性要求,引入DSP核会使SoC的芯片成本大为增加, 所以本文将MPEG-4的解码电路作为SoC芯片中的一个硬件加速模块来实现。

在手持设备应用中, MPEG-4 视频简单层(Simple Profile) 最为常用, 而其中计算量最大的部分是反离散余弦变换( Inverse Discrete CosineTransform ) , 所以反离散余弦变换的实现是加速MPEG-4 解码的关键。有很多优秀的设计专门以处理IDCT为目标.本文描述的MPEG-4解码加速器基于AMBA 总线, 作为高速总线(AHB) 上的一个主设备, 对四个亮度块(block) 和两个色差块组成的宏块(macrob lock) 一起做IDCT 运算, 并根据配置完成IDCT前的反量化和IDCT后运动补偿的图像叠加, 最终将结果写回显存。整个过程高度并行处理。

本文第1部分主要介绍IDCT快速算法的选择和优化, 第2部分讨论硬件结构和设计技巧, 第3部分介绍仿真验证和综合结果。

1 二维DCT?IDCT 算法描述及快速算法的选择和优化

1.1 算法描述

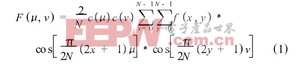

对于输入矩阵f (x , y ) {0≤i, j N }, 它的离散余弦变换式如下:

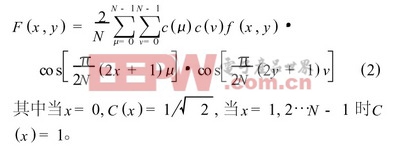

反变换式如下:

直接计算IDCT , 每个象素点f ( i, j ) 都需要计算N2次乘法, 一个块有N2 个象素点, 总共需要N4 次乘法计算, 因此计算量相当大。

1.2 快速算法的选择

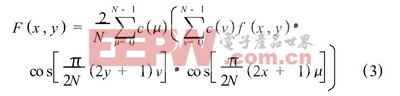

二维IDCT 可以写成:

上式括号内是对F (u, v ) 的一行作一维IDCT 变换, 括号外是对行IDCT 的结果做一维列IDCT变换。如不考虑系数2/N , 二维的IDCT 就分解为对矩阵F (u, v ) 先做行IDCT 再做列IDCT 的2N 次一维IDCT 变换。(本文中取N = 8)。

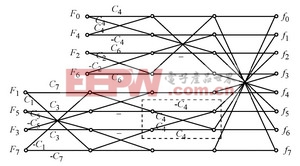

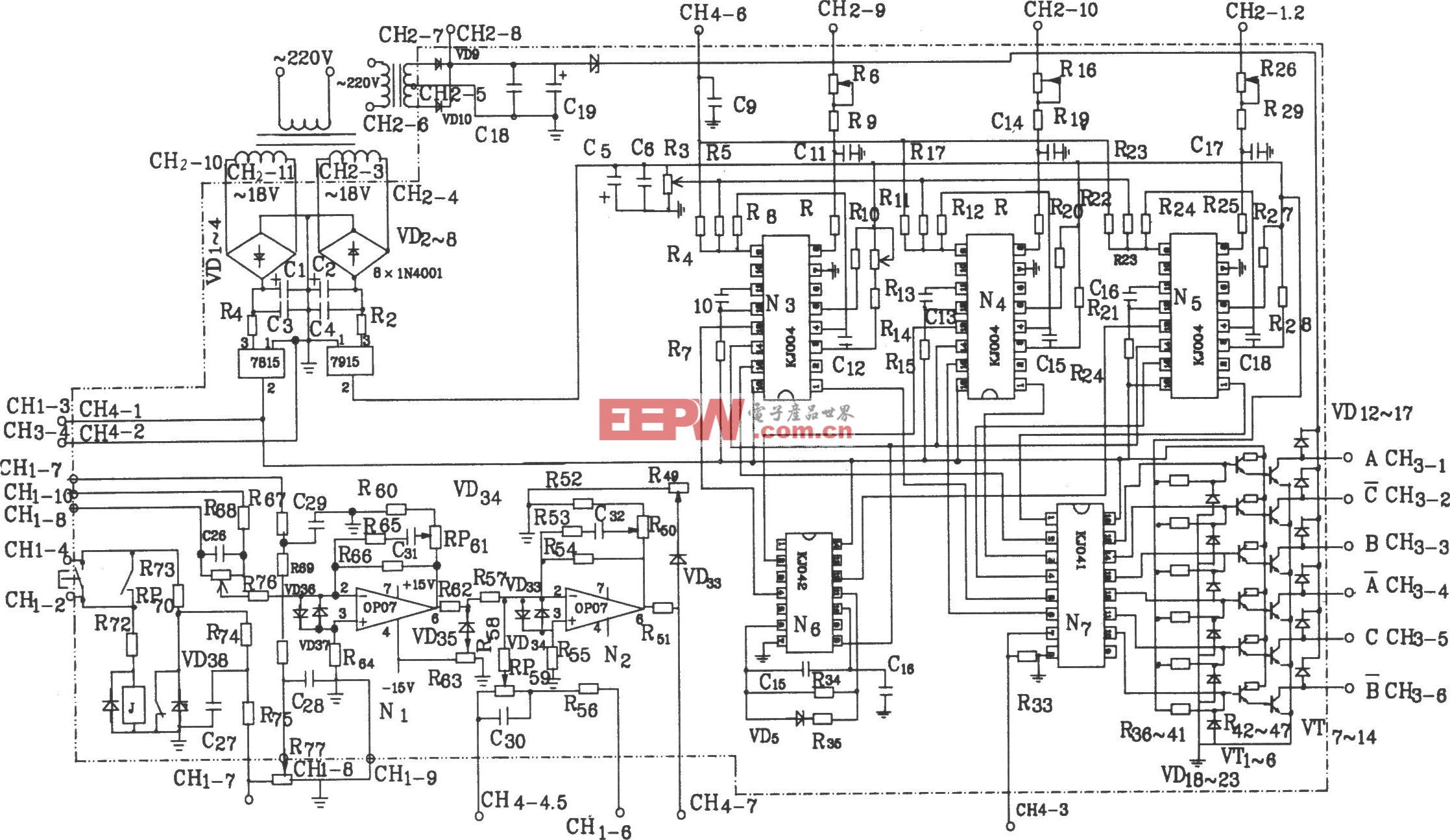

对于一维IDCT 有许多优秀的快速算法。其中一种是将IDCT 原始的变换矩阵分解成几个利于计算的变换矩阵, 然后逐步计算。还有一种是利用了IDCT的奇偶对称性以及余弦函数的和差化积性质最大程度的共用乘法器。虽然后一种的乘法次数为12次, 少于前一种的16次,但由于前一种的乘法集中在输入附近, 也就是说绝大部分乘法的其中一个乘数是输入F(k ) , 因而可以通过提前判断输入F(k ) 中是否有较多的0 元素从而直接跳过一部分的乘加运算, 达到加速的目的。MPEG-4 解码的IDCT 输入中, 有大量的0, 所以前一种的算法更有利于MPEG-4 解码。其算法流程如图1。

图1 chen 算法流程Ci= cos( iπ/16)

评论