UPD78F0411 时钟控制(2)

注复位释放后该标志只能被修改一次。如果已经设置了该项,则无需再设置。

注意事项供电电压达到所用时钟的操作电压后,设置时钟(参见第二十七章电器特性(标准产品)) 。

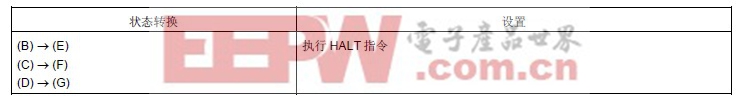

(10) CPU 使用内部高速振荡时钟(B)时HALT 模式(E)的设置。

CPU 使用高速系统时钟(C)时HALT 模式(F)的设置。

CPU 使用副系统时钟(D)时HALT 模式(G)的设置。

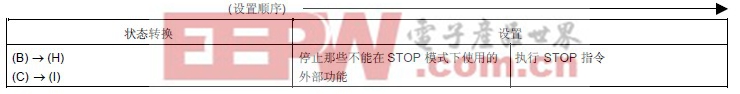

(11) CPU 使用内部高速振荡时钟(B)时STOP 模式(H) 的设置。

CPU 使用高速系统时钟(C)时STOP 模式(I) 的设置。

备注1. 表5-5 的(A) 到(I)对应图5-15 的(A)到(I)。

2. EXCLK, OSCSEL: 时钟操作模式选择寄存器(OSCCTL)的第7 和6 位

MSTOP: 主OSC 控制寄存器(MOC)的第7 位

XSEL, MCM0: 主时钟模式寄存器(MCM)的第2 位和第0 位

CSS: 处理器时钟控制寄存器(PCC) 的第4 位

1.7 CPU 时钟切换之前的状况与切换之后的处理

CPU 时钟切换之前的状况与切换之后的处理显示如下。

1.8 CPU 时钟和主系统时钟切换所需的时间

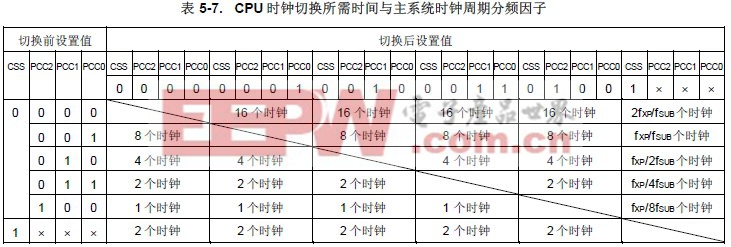

通过设置处理器时钟控制器(PCC)的第0 位到第2 位(PCC0 到PCC2)以及第4 位(CSS),可以切换CPU 时钟(在主系统时钟和副系统时钟之间),同时可以改变主系统时钟的分频比。

修改PCC 后,实际的切换操作不会立即执行;使用切换前的时钟继续操作几个时钟(见表5-7)。

可以通过PCC 寄存器的第5 位(CLS)来确定CPU 使用主系统时钟还是副系统时钟。

注意事项主系统时钟周期分频因子(PCC0 到PCC2)的选择,以及从主系统时钟到副系统时钟的切换(CSS 从0 变到1)不能同时设置。

但对于主系统时钟周期分频因子(PCC0 到PCC2)的选择,以及副系统时钟到主系统时钟的切换(CSS 从1变到0)可以同时设置。

备注1. 表5-7 列出的时钟数是切换前的CPU 时钟数。

2. 将CPU 时钟从主系统时钟切换到副系统时钟,可通过舍入一个时钟并舍弃小数部分来计算时钟数量(如下所示)。

示例: 将CPU 时钟从fXP/2 切换到fSUB/2 (@ 振荡频率fSUB = 32.768 kHz, fXP = 10 MHz)

fXP/fSUB = 10000/32.768 ≌305.1 →306 个时钟

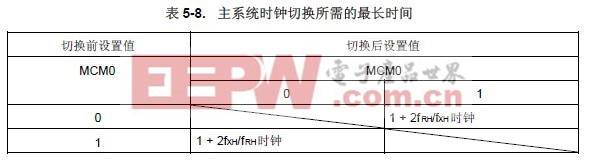

通过设置主时钟模式寄存器(MCM)的第0 位(MCM0),可以切换主系统时钟(在内部高速振荡时钟和高速系统时钟之间)。

修改MCM0 后,实际的切换操作不会立即执行;使用切换前的时钟继续操作几个时钟(见表5-8)。

可以通过MCM 寄存器的第1 位(MCS)来确定CPU 使用内部高速振荡时钟还是高速系统时钟。

注意事项当内部高速振荡时钟切换到高速系统时钟时,MCM 的第2 位(XSEL)必须预先被设置为1。XSEL 值在复位释放后只能被修改一次。

备注1. 表5-8 所列时钟数是切换之前的主系统时钟数。

2. 通过舍去小数部分,计算表5-8 的时钟数。

示例: 将主系统时钟从内部高速振荡时钟切换到高速系统时钟(@振荡频率fRH = 8 MHz, fXH = 10MHz)

1 + 2fRH/fXH = 1 + 2 x 8/10 = 1 + 2 x 0.8 = 1 + 1.6 = 2.6 → 2 个时钟

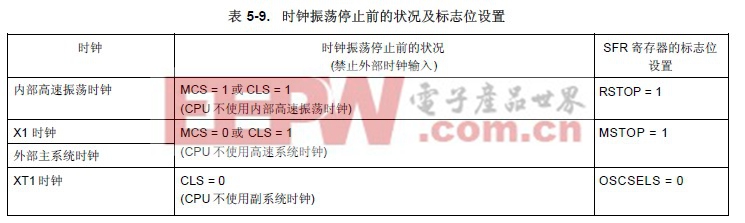

1.9 时钟振荡停止前的状况

下表列出了停止时钟振荡的寄存器标志位设置(禁止外部时钟输入)和时钟振荡停止前的状况。

1.10 外部硬件与源时钟

下表列出了78K0/LC3 中包含的外部硬件与源时钟。

注1.当CPU 使用副系统时钟且内部高速振荡时钟已经停止时,不要启动依赖由外部硬件引脚输入外部时钟的这些功能。

2.仅对 UPD78F041x。

备注Y: 可选, N: 不可选本文引用地址:http://www.eepw.com.cn/article/170631.htm

评论