基于BiSS协议的光电编码器通信模块设计

主机输出寄存器地址序列后,如果是读寄存器模式,即寄存器地址序列中的WNR位为0,MA继续输出时钟,SL返回寄存器中的数据。如果是写寄存器模式,即寄存器地址序列中的WNR位为1,MA则继续输出高低占空比信号,SL返回写入的寄存器值,如该值与发送的数据一致,说明写寄存器操作成功。本文引用地址:http://www.eepw.com.cn/article/169493.htm

位置数据、寄存器数据、寄存器地址后均加有CRC校验,保证传送数据的准确性。对于总线连接方式,BiSS协议给出了多编码器串行连接的读数方式和寄存器读写方式,是上述时序的组合,详细说明见参考文献[1]。

2.1 硬件设计

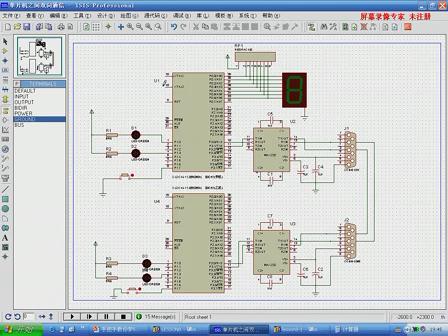

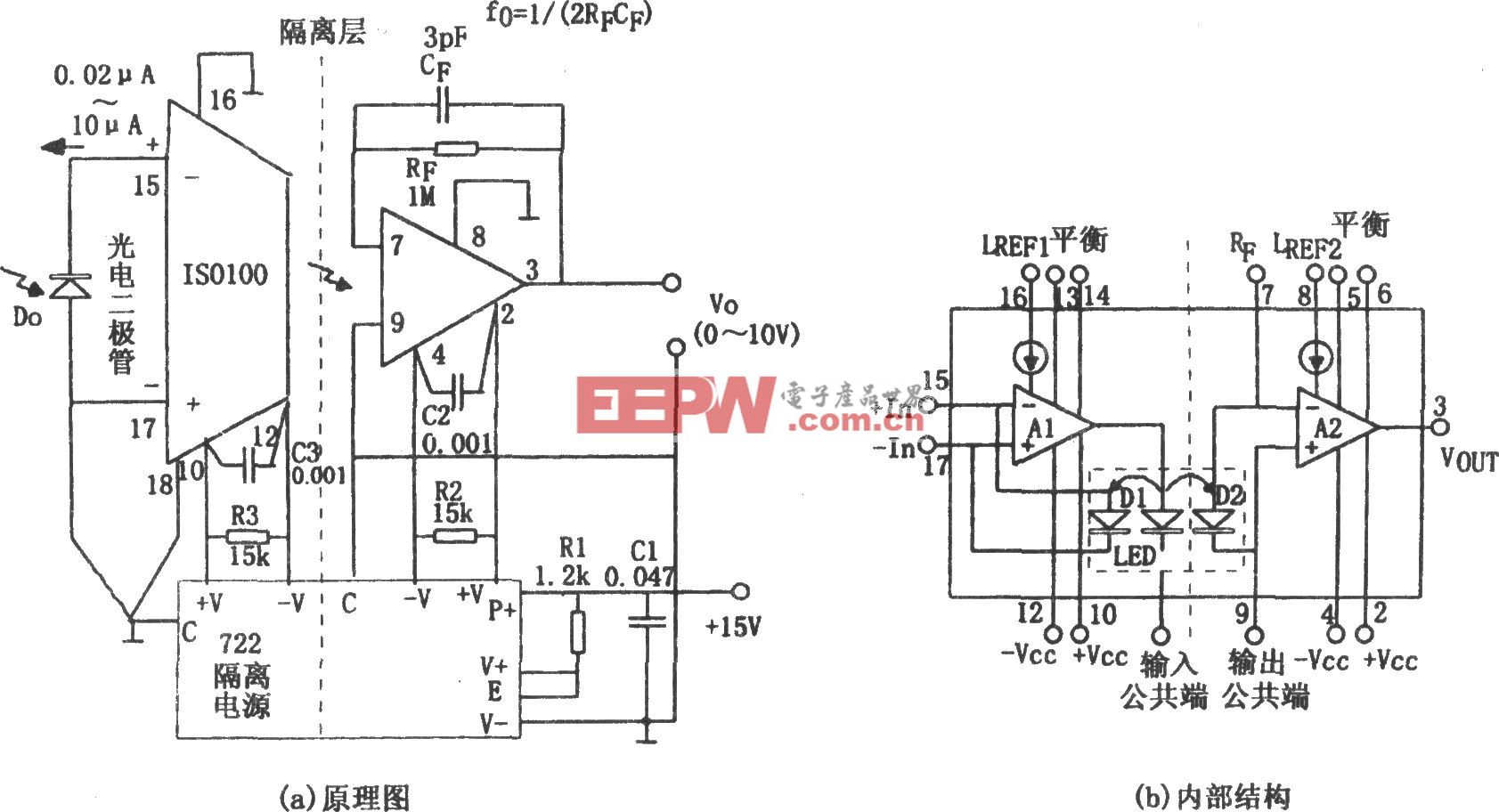

通信模块基于EP1C12Q240-FPGA设计,对Netzer RE252型号的绝对位置式光电编码器进行位置读数,采用点对点连接,RS422差分总线接口使用MAX3460电平转换芯片。为了提高通信模块在工业应用中的抗干扰性,接口芯片和FPGA核心模块之间加入高速光耦HCPL0630进行隔离。输出接口有并行接口、串行通信接口、增量式等,与上位机通信。

2.2 软件设计

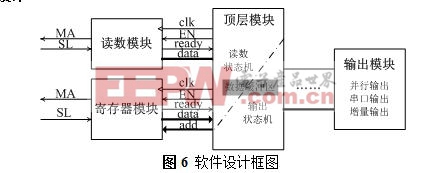

程序在Quartus II软件[6]环境下,使用Verilog HDL[7]语言编写,采用的是自底向上的编写方式,使用约6000门资源。底层模块包括读数模块、读写寄存器模块。底层模块的clk时钟由顶层模块的锁相环PLL分频提供[8]。读数模块或者读写寄存器模块在EN置位后,独占MA线,发送与协议对应的波形,再根据编码器返回的SL波形采样识别数据,通过data总线保存到顶层模块的数据缓冲区。

顶层模块主要包括两个状态机。读数状态机根据编码器的工作时序要求完成寄存器的初始化,然后不断的读取编码器的数据保存到数据缓冲区。输出状态机根据指定标志位从数据缓冲区读取数据,控制以并行、串口、增量式的输出时序逻辑。

3、实验结果及对比

quartus II中的signalTap逻辑分析仪可以嵌入到FPGA,观察管脚电平和内部变量值。图7所示为编码器返回14位数据的通信波形。从图中可见,SL的第一个下降沿即ACK位延迟了约0.65μs,为总线延时。一个完整的读数操作从-5时刻开始需要约210个采样点,即4.2μs的时间(4.2μs=210*1/50 MHz,采样频率50MHz)。

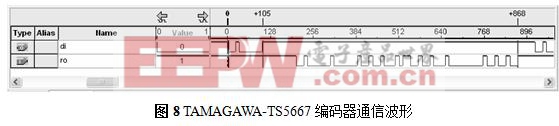

图8为TAMAGAWA-TS5667型号的绝对式光电位置编码器返回17位数据的通信波形,该编码器采用起止式异步串行通信协议,波特率为2.5M。半双工通信方式下,一个完整的读数操作从0时刻di请求开始,到约868时刻ro应答结束,需要约30.4μs的时间(30.4μs=868*1/28.57MHz,采样频率28.57MHz)。

BiSS协议下的数据位数可调整,如果把BiSS协议下的数据位数从14位增加到17位,只需增加3个时钟的时间长度,在10Mbps下为0.3秒。

由此得到,在同样传输17位光电编码器位置数据的情况下,起止式异步协议耗时30.4μs,而BiSS协议仅耗时4.5μs,通信速度提高了6.75倍。

4、结论

基于BiSS协议的各方面优点,目前已有德国IC-Haus,美国Danaher,以色列Netzer Precision等130多家公司申请并免费使用了BiSS协议,BiSS协议得到了越来越广泛的应用。同时,BiSS与SSI协议下的接口兼容,方便SSI使用者和厂商系统升级。综上所述,BiSS协议在降低协议成本、硬件成本,提高通信速度和准确率等综合方面,是未来编码器用串行通信协议中一种非常理想的选择。

评论