基于FPGA高速实时数据传输系统设计方案

.引言

本文引用地址:http://www.eepw.com.cn/article/169485.htm信息时代的日新月异,催促着各种各样的数据信息快马加鞭,人们在要求信息传输得越来越快的同时,还要求信息要来得更加及时,于是高速实时的数据传输就成为了电子信息领域里一个永远不会过时的主题。但是,可以清楚地看到,当今动辄成百上千兆的数据流一股脑的涌入,任何一个高速数据传输系统的稳定性和安全性等方方面面的问题都面临着极大的挑战,稍有考虑不周之处就会引起各种各样的问题,因此如何能安全高效的对高速数据进行实时接收、存储、处理和发送正是此次设计方案的目的。

2.设计方案的硬件选定

鉴于当前高速数据传输系统的设计方案大多是现场可编程门阵列(FPGA)加片外存储介质( SDRAM、SRAM、DDR等)的组合,于是本次设计方案同样采用这种组合方式,具体为一片 FPGA、三片静态存储器( SRAM)和一片高速数据传输芯片。 FPGA具有管脚多、内部逻辑资源丰富、足够的可用 IP核等优点,用作整个高速数据传输系统的控制模块极为合适,此次方案中选用 Altera公司的高性价比 Cyclone[2]系列 FPGA;静态存储器具有昀大的优点就是数据读取速度快,且控制信号简单易操作,昀适用于高速数据存储介质,方案选用 ISSI公司的 IS61LV51216型号的静态存储器 [3],其处理速度和存储容量满足系统设计的需要;TI公司的 TLK1501[4]是此次设计选用的高速数据传输芯片,其传输能力十分强大,不仅能满足当前设计的传输速度需要,还留有充分的带宽余量,为以后的系统改进提供了条件。上述三种芯片是此次高速数据传输系统所要用到的主要组成部件,其具体连接方式等问题不作讨论。

3.具体设计方案

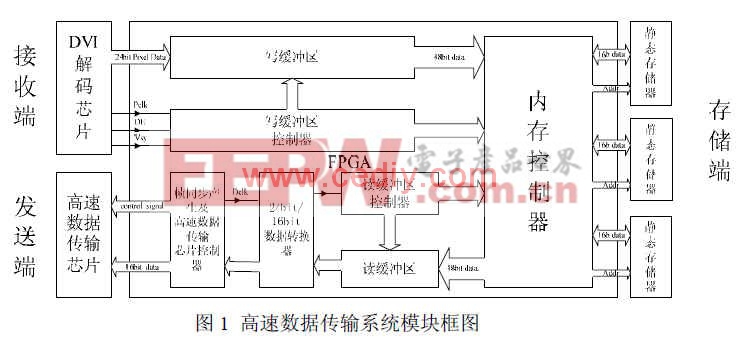

实现整个数据流从接收、存储、转换直到发送的过程由图一可以看出,在接收端经由 DVI[1]解码芯片传输的解码数据包含 24bit并行像素数据和三个同步信号――像素时钟 Pclk、数据使能信号 DE以及场同步信号 Vsy,fpga内部的写缓冲区控制器则会根据以上三个数据同步信号生成写缓冲区的写入地址,控制 24bit的像素数据信号存入写缓冲区中,并会在一段时间后向内存控制器发送读请求( wcache_rreq)以读出写缓冲区内的已写入数据,写缓冲区是由 fpga自带的 M4K块配置生成的双端口 RAM结构[2],采用乒乓操作,这样整个内存读取和缓冲区写入过程是各自独立进行的,保证所写入数据的完整性,内存控制器在接收写缓冲区控制器发送的读请求后,按照相应的写缓冲区地址读取数据,并将其写入片外静态存储器中,以上为像素数据的接收和存储过程;在发送端,帧同步产生及高速数据传输控制器通过 fpga自带的锁相环产生数据时钟 Dclk、帧同步 Fsy等信号,使读缓冲区控制器产生对读缓冲区的读取地址,读缓冲区控制器在产生读地址的同时,还会在一段时间间隔后向内存控制器发送写请求( rcache_wreq)以向被读过的读缓冲区部分写入新数据,同样读缓冲区也是双端口 RAM结构,采用乒乓操作,保证被发送数据的连续完整,被读出的 24bit数据经过一个 24bit/16bit数据转换器转换为 16bit并行数据之后才能输出给高速数据传输芯片,而内存控制器在接收读缓冲区控制器的写请求后在片外静态存储器中读出相应地址的数据写入读缓冲区中,这样整个数据的接收、存储、转换到发送的过程得以实现。

3.1 写缓冲区控制器的设计

评论