基于DVI接口的LED视频控制系统研究

EDID数据存放在DVI解码电路的AM24LC02芯片中,该芯片为2Kb(256×8),I2C 总线、CMOS工艺的串行EEPROM存储器。电源VCC的范围为 2.7V~5.5V,可以通过把 WP引脚接电源来对整个存储器写保护,此时,存储器的内容不可更改。将DVI接口插座的第16脚(热插拔检测端)通过1KW上拉电阻和第14脚(+5V电源端)相连,构成显示设备的HPD (热插拔检测)信号。AM24LC02芯片的时钟线(SCL)、数据线(SDA)和DVI接口插座的第6、7脚相接,当系统上电时,AM24LC02 在时钟 SCL 的同步控制下通过 DDC 通道向PC机传送 EDID数据。只有当PC机识别和正确配置后,TDMS链路才会被激活。

TFP101A 是一种T.M.D.S.信号接收芯片,通过检测DE信号的状态转变来确定链路的激活状态。如果106个像素时钟过后,DE状态未发生变化,则认为链路未激活,输出SCDT (同步检测指示信号) =0;在SCDT=0的情况下,如果发现在1024个像素时钟内DE信号有两次转变,则认为链路已激活,输出SCDT=1。RX2-和 RX2+表示红色数据的差分信号,RX1-和 RX1+表示绿色数据的差分信号, RX0-和 RX0+表示蓝色数据的差分信号,分别与DVI接口的单链路通道相接(1、2、9、10、17、18脚);RXC-和 RXC+是表示时钟的差分信号,与链路时钟相接(23、24脚)。TFP101A内部锁相环回路从时钟通道获得同步时钟,为后继的T.M.D.S.码元数据恢复、像素时钟同步以及T.M.D.S.信号解码提供参考时钟,同时也作为前端锁存器对输入信号进行4倍过采样的参考时钟,T.M.D.S.解码器将 10位的串行T.M.D.S.编码解码成8位并行像素数据以及相应控制信号,并从输出接口电路将像素数据、控制信号、场同步信号和行同步信号并行输出。

数据处理与显示控制模块

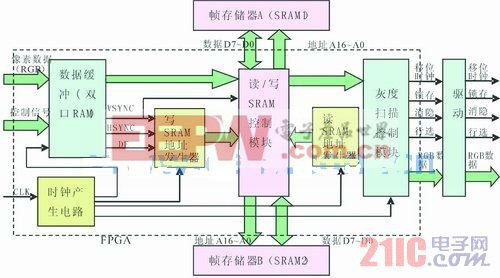

数据处理与显示控制模块主要负责对显示数据作进一步地转换、处理,产生符合 LED显示屏灰度级显示的数据,并将其送入驱动电路。数据处理与显示控制模块原理图如图2所示,主要由数据缓冲处理(双口RAM)、读/写控制、灰度扫描控制、驱动4部分组成,SRAM1、SRAM2 作为帧数据存储器。

图2 数据处理与显示控制模块原理图

评论