TMS320C5402在16路全双工来电显示中的应用

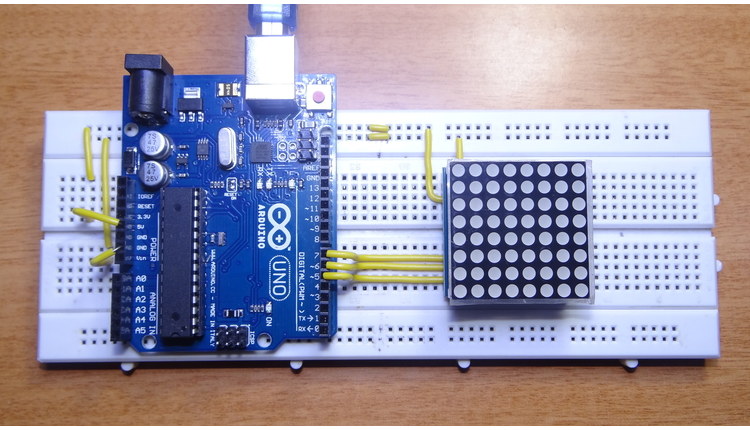

1.2 解调部分

在图1中,k一定要小于每个比特的采样数,此例k6。假设接收到的样值s(n)和s(n-k)属于同一个比特,则:

v(n)=s(n)s(n-k)=A2sin(2πFnTe)sin(2πF(n-k)Te)

=A2/2[cos(2πFkTe)-cos(4πFnTe-2πFkTe)]

通过低通滤波器后,r(n)=A2/2cos(2πFkTe) F={F0,F1}

由此可见,r(n)为常数,A2/2cos(2πF0kTe)或A2/2cos(2πF1kTe),仅依赖于发送比特是“0”还是“1”。

k的选择应使d(k)=|cos(2πF0kTe)-cos(2πF1kTe)|最大。在此方案中,k=4。

由于v.23的比特率为1200bps,因此低通滤波器fcutoff=1200Hz。

2 DSP设计

TMS320C5402是一款高性价比的数字信号处理器。片上有可编程等待状态发生器和块切换寄存器、两个多通道增强型缓冲串口(McBsp)、一个增强型的8位并行主机接口(HPI8)、两个16位定时器、一个六通道DMA控制器。TMS320C5402还有4K×16bit片上ROM和4K×16bit片上RAM,最大可寻址1M×16bit的存储空间。片上ROM的保留区域对用户来说是不可用的,原因是用户无法写入数据。片上ROM包括为Bootloader保留的区域及A律表、μ律表、sin表和中断向量表。TMS320C5402有内部振荡器构成的内部时钟源和锁相环时钟发生器构成的外部时钟源。

系统初始化工作频率为100MHz,对片上存储器访问无需等待状态,访问外部I/O空间设为两个等待状态。

在本系统中,采用McBsp0、DMA0、DMA4。DMA0的同步事件为McBsp0的接收事件REVT0;源地址指向DRR,并固定不变;目的地址指向DMA接收缓冲区,每次自增1;采用ABU模式实现双缓冲,DMA0接收缓冲区半满或全满时发生中断;中断服务子程序对其中刚引起中断的那一半数据进行解调,而此时接收的数据顺序放到另一半。为了节省存储器空间,串口不对接收数据进行扩张,而在程序中进行软件扩张。DMA4的同步事件为McBsp0的发送事件XEVT0;源地址指向DMA发送缓冲区,每次自增1;目的地址指向DXR,并固定不变;采用ABU模式实现双缓冲;DMA发送缓冲区半满或全满时发生中断,中断服务子程序发送刚引起中断的那一半数据,而此时正在调制的数据顺序放到另一半。因为线路上一般传送的是A律数据,因此发送时要在串口中进行硬件压缩。

经仿真发现,采用C语言编程,TMS320C5402至少可以实现16路全双工来电显示,因此McBsp0应设置为:接收数据格式为每帧8字,每字16位(表示16路A律数据);发送数据格式为每帧16字,每字16位。为了减少串口错误,指定由RSYNCERR和XSYNCERR产生RINT和XINT。

另外还需注意,为了实现字同步,异步传输时首先对发送数据的每个字节加上起始位“0”和停止位“1”,解调后应去掉相应的起始位和停止位。在发送过程中,如果没有待发数据,可以发送停止位(即频率为F1的载波)或静音(样值为0)。

利用TMS320C5402实现符合v.23建议的16路全双工来电显示,其原理简单,易实现,但是抗干扰性较差。由于DTMF的某些频率与v.23码的载波频率非常接近,如果混有DTMF码,也可解出少量的DTMF码。为了排除此类错误,需要加上增益控制、带通滤波等,这使得设计变得复杂。实践中,此类错误较少,除非特别要求,否则不必理会。

为了进一步提高精度,可以用长整数表示相位,还可以采用重采样技术及局部FFT等技术[5]或者改进解调方法可实现高精度检测。

评论