米波段DBF体制雷达数字接收机的实现

在整个雷达系统联调之前,由一块内定时板给数字接收机提供调试时需要的定时时序。当整机联调时,整个雷达系统的其他分系统-波形产生、接收前端等也需要定时时序(如图1所示),此时对整个雷达系统提供定时时序的为一块功能更为强大、接口更加丰富的外定时板。为了使两套定时时序不互相冲突,在二次底板上使用一组Mux,根据上位机命令选通内、外定时,从而决定整个系统的定时时序是由内定时板产生还是外定时板产生(图3)。

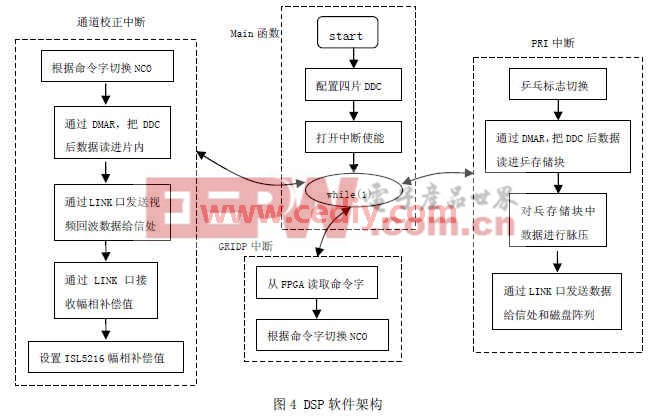

2.3 数字接收机软件的实现

TDRB0的DSP不仅要完成对三块DDC的配置,10个通道ISL5216后数据的缓存、重排,还要完成雷达信号处理中的脉压运算,并把脉压后数据通过LINK口传给信号处理机。由于数字接收机同雷达系统的定时时序紧密相关,因此DSP的软件架构采用中断驱动而不是数据流驱动的方式,如图4。经过优化,用DSP完成一个通道的脉压处理(1024点频域脉压加512点频域脉压)一共需要750μs,对于米波段雷达,其PRI通常为几个ms左右,那么在一个PRI时间内,有足够的时间完成10个通道的脉压处理。

DBF体制雷达中,通道间幅相不一致会导致天线方向图的旁瓣会升高[2],信噪比降低,严重影响空域滤波效果。当已经知道通道间幅度和相位误差后,对回波数据乘以校正因子即实现多通道的幅相校正。由于雷达通道数较多,直接在ISL5216中设置校正因子进行幅相校正,与在信号处理机中利用DSP进行多通道的幅相校正相比,可以大幅度减小运算负荷。因此在通道校正中断中,每块TDRB0需要从信号处理机获得校正因子,具体如图4所示。本文引用地址:http://www.eepw.com.cn/article/166883.htm

数字接收机利用上位机通过PCI总线给TDRB0加载DSP程序,由于PCI总线的共享性,DSP程序不是同步开始工作。为了保证板间数据始终同步,要求定时时序要在所有板卡的DSP程序都加载之后才能提供,这样所有TDRB0的DSP同时进入PRI中断,从而保证板间数据的同步。这种先后顺序是通过上位机对二次底板上Mux模块的控制来屏蔽、选通外定时模块所产生的时序来实现的。

3 结论

本文作者创新点:1.结合某型米波段DBF体制雷达的研制,提出了一种基于CPCI总线的数字接收板卡TDRB0,其具有集成度高、模块化强、动态范围大等特点,通过在外场长时间检验,也证明其具有良好的可靠性。已对工作在雷达系统中的每个通道进行了反复测试:当输入200Mhz以上信号在300khz带宽情况下, ENOB达到10.9bit,动态范围典型值为88dB,DDC滤波器带外抑制度到70dB以上,带内纹波小于0.03dB。2.以多块TDRB0为核心,辅以定制的二次底板、内外定时模块,定时切换模块、SCSI数据采集机箱等调试设备,组成了一个便于工程应用的数字接收机,方便了外场联调,加快了项目进度。实践证明,该数字接收机满足了项目要求,达到了预期目的。

评论