米波段DBF体制雷达数字接收机的实现

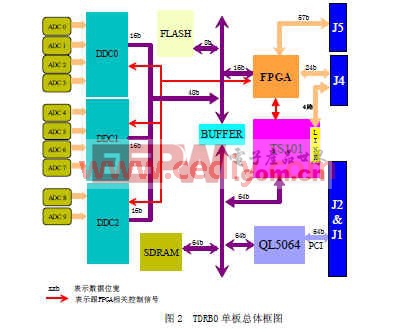

TDRB0的特点之一为通道较多,故选用专用DDC芯片完成数字下变频和抽取滤波等功能,与FPGA实现DDC功能相比,具有开发周期短、每通道性价比较高等优势。这里选用ISL5216,其单片集成4个独立可编程数字下变频通道,数据带宽1Mhz,可实现单级最多256阶的FIR,因此非常适合米波段雷达的窄带信号数字滤波。为了完成10通道的数字接收,可采取如图2所示拓扑,即DDC0和DDC1各处理四通道,而DDC2只处理2个通道。本文引用地址:http://www.eepw.com.cn/article/166883.htm

现代的数字接收系统还会要求具有一定的预处理功能,以减轻后续数据传输和处理的压力。TDRB0采用DSP作为数据处理单元,DSP+FPGA作为数据传输单元,具有较强的运算能力和IO互连能力。考虑到雷达系统通常需要较大的动态范围和较高的运算精度,目前大部分雷达系统数字信号处理模块都选用浮点型DSP器件,以及ADI公司TigerSHARC系列DSP所具有的超强浮点运算能力和IO互连能力,我们选择TS101作为TDRB0的处理、存储和数据传输的中枢。

TDRB0的对外接口很多,分布于前面板和J1~J5。TDRB0数据后续传输的通路有三条:①PCI总线。TDRB0基于CPCI总线,利用半定制芯片QL5064实现了66Mhz、64bit PCI接口。②TS101自己的四路LINK口,通过J4和二次底板与其他板卡的TS LINK口通讯,其传输速率可达到150MB/s;③FPGA连接在J4和J5上共81 bit IO管脚,可自定义用,也可用于最大传输速率320MB/S的FPDP总线。

2.2 数字接收机平台的搭建

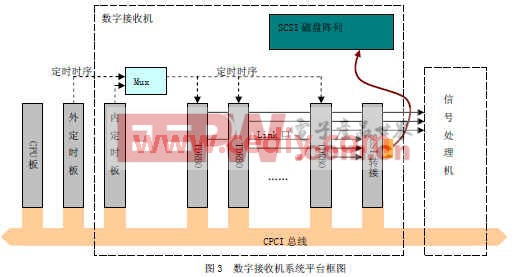

在米波段DBF体制雷达中,由多块TDRB0组成的数字接收机,与由多块信号处理板卡组成的信号处理机共用一个21槽位的标准6U CPCI机箱。如果采用TDRB0的PCI通道给信号处理机传送数据,可以不用再设计定制的二次底板,但是在本系统中,要求的传输数据率较高,共享型的PCI总线难以承担如此负荷。采用DSP的LINK通过二次底板传数,构成一套专用LINK总线,能够保证传输带宽,并且实现起来也较为灵活方便。同时,通过二次底板, TDRB0接收定时板送过来的定时信号和雷达命令字(如图3所示)。

为了能够离线分析雷达实际的回波数据,数字接收机中还包括一个SCSI磁盘阵列,能够实时的把各通道数字接收后信号存储下来。通过一套SCSI转接板卡,数据从TDRB0经过二次底板流向磁盘阵列。数字接收机存在两套专用LINK总线,一套连接多块TDRB0和信号处理机,数据传给信号处理机,完成正常的雷达信号处理;另一套连接多块TDRB0和SCSI转接板卡,把数据通过转接板卡送给磁盘阵列存储。两套总线之间互不影响,因而既可同时工作,也可单独分开工作。

评论