基于ADSP-BF5619处理的H.264视频编码器设计

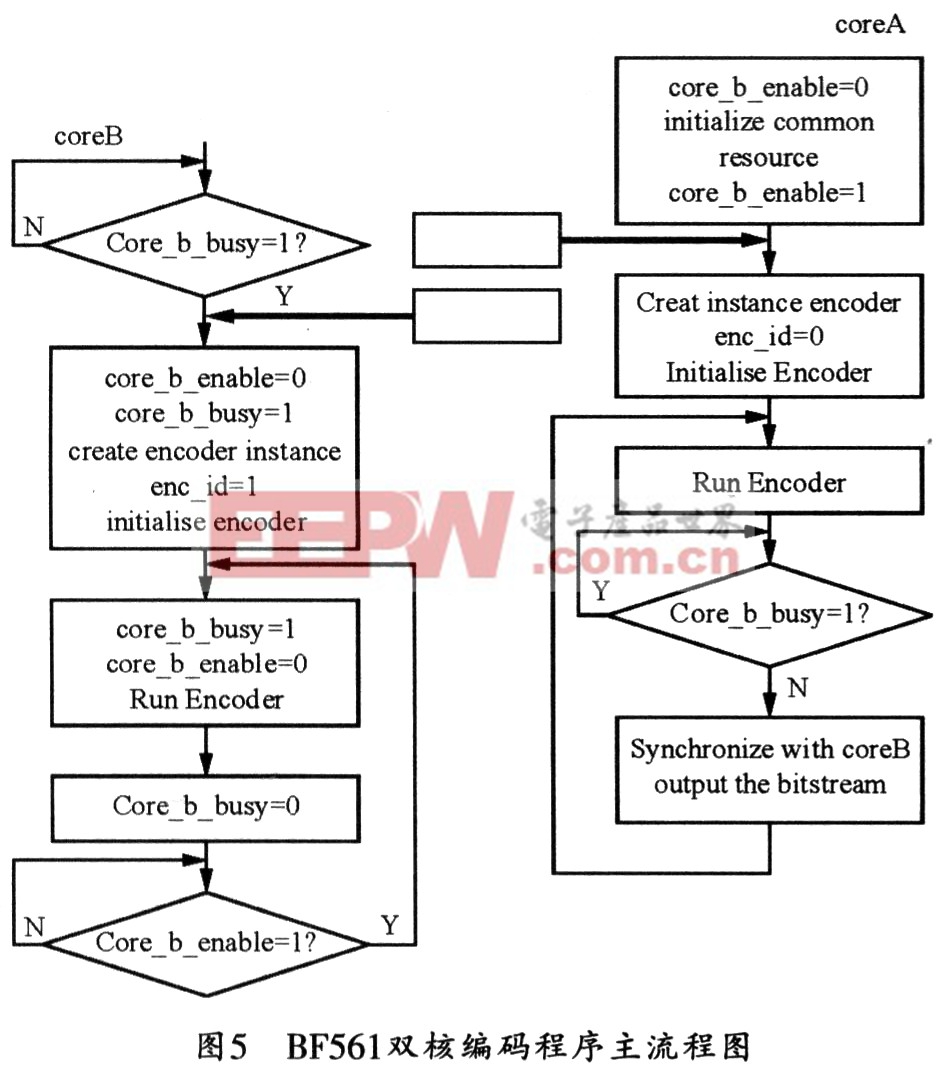

在ADSP-BF561开发板上实现这个编码算法时,其主要的难点是两个核之间如何通信以及协调工作。双核同时运行一个视频编码程序时,需要对数据进行共享和交换。虽然,使用片外内存或者L2共享存储器来进行宏块数据交换的实现方法比较简单,且不需要进行数据的拷贝,但是,大量访问低速率存储器的操作将极大地影响程序执行的速率,进而影响编码器的编码效率,所以,不能采用共享内存来进行宏块数据的交换。本文采用的是IMDMA在双核各自的L1数据段直接进行数据交换,而且在编码处理的同时进行内存数据的交换,从而避免了大量访问低速率的存储空间操作,减少了程序执行的时间。而由于消息交换数据量很小,可以使用共享存储器,因此,可以采用访问速率相对较快的L2存储器来进行存取。事实上,笔者已经经过优化编程在BF561开发板上实现了上述编码算法。其双核编码主流程如图5所示。本文引用地址:http://www.eepw.com.cn/article/166848.htm

3 试验结果与数据分析

经过优化,H.264的编码性能有了较大的提升,实现了在BF561芯片上对4CIF格式视频的实时编码处理。同时,笔者还在VisualDSP++5.0编译环境下分别对原编码器和双核编码器实现的编码结果进行了测试,其结果如表1所列。事实上,编码速度基本取决于图像画面的运动情况和颜色是否丰富。从上面的数据可以看出,对于不同序列,其编码速度也不同。Claire序列的编码速度之所以很快,是因为图像背景静止,只有肩部和头部有运动,所以编码数据量较表1对不同序列的优化结果(25f/s CIF格式)少,编码速度较高。另外,如果图像比较简单,其编码速度也会较高,从而节约编码时间。

试验结果表明,采用本文的优化方法可以节约大量的H.264视频编码数据处理的时间,能较好地满足4CIF视频序列实时编码的要求。而对于很复杂的图像,也可以在一定的量化参数下实现4CIF的实时编码。

4 结束语

本文重点研究了基于ADSP-BF561双核处理器的H.264视频编码算法的优化及其实现方法。同时针对ADSP-BF561双核处理器的体系结构,对编码的关键部分进行了算法流程的调整,并通过BF561双核之间的数据交换和协调工作,在双核上实现了4CIF格式视频数据的实时编码。实践证明,使用VisualDSP++5.0仿真软件,在ADSP-BF561开发板上实现25f/s的H.264 4CIF视频编码系统,可以满足人们对视频传输的需求。

评论