AM-OLED显示驱动芯片中内置SRAM的设计

2 SRAM电路的低功耗设计

嵌入式SRAM的功耗大致分为动态功耗和静态功耗。对应到SRAM的具体模块上,其功耗主要消耗在译码器、字线驱动、位线预充、灵敏放大器以及静态漏电流上。译码器可以用与非门逻辑来代替伪NMOS逻辑设计以降低功耗,由于本电路结构没有灵敏放大器电路,因而无需考虑其功耗。下面主要就动态功耗进行优化。

SRAM电路的动态功耗计算公式如下:

式中,iactive为工作单元的等效电流;ileak为不工作单元的漏电流;CDE为每个译码器的输出节点电容;VINT为内部电源电压;iDC为读操作消耗的直流电流;△t为直流电流的激活时间;CPT为CMOS逻辑电路和外围电路的总电容;IDCP为外围电路的静态电流。本文分别从降低位线寄生电容及其电压摆幅来降低SRAM的整体功耗。

2.1 降低寄生电容

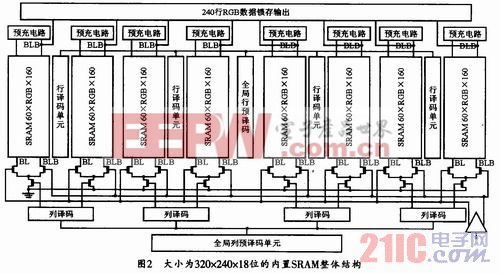

降低寄生电容可采用位线划分技术(DBL)和字线划分技术(DWL),即将位线和字线划分成多级,以降低位线寄生电容和字线寄生电容,这样即可降低读写功耗,也能提高数据的读写速度,进一步提高SRAM的整体性能。图2所示是一个大小为320x240x18位的SRAM存储阵列的整体结构。该结构将240x18列分成4块,每块包含60x18位数据;320行则分成左右两级,每级含160行。这样就把整个阵列分成了8个小模块,每块大小为160x60x18位,这样就使得字线电容降到了原来的1/4。位线电容则降为原来的1/2。本文引用地址:http://www.eepw.com.cn/article/166194.htm

2.2 降低位线电压摆幅

由于传统结构中,整个读写过程的预充电路都会对两条位线进行预充电,故会造成功耗的浪费。而读电路是采用单边输出,位线上的电压摆幅则必须采用全摆幅形式,因此,只能通过降低写操作时的电压摆幅来降低功耗。

评论