基于PCIe总线的航空视频采集记录系统的设计

2.3 视频数据回放

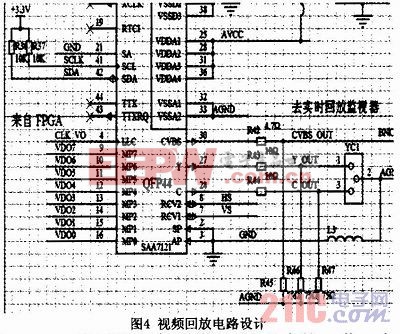

视频回放是方便飞行员能够实时监控训练和试验的情况。系统采用Philips公司的SAA7121视频编码器,将FPGA处理后的视频数据转换为PAL制的综合视频,送给飞行员面前的监视器进行显示。如图4所示。本文引用地址:http://www.eepw.com.cn/article/165890.htm

SAA7121需要进行初始化配置后才能工作,初始化通过设置编码器的寄存器,配置其工作模式。初始化要通过I2C总线完成,系统的I2C总线接口由FPGA实现。同步时钟CLK VO和8-bit并行视频数据都是由FPGA解码处理后传输过来的。编码器的工作频率为27MHz,FPGA解码后的视频数据经过SAA7121编码器的综合视频信号CVBS送给监视器。同时也设计了一个备用的YC分量视频接口。

2.4 视频传输

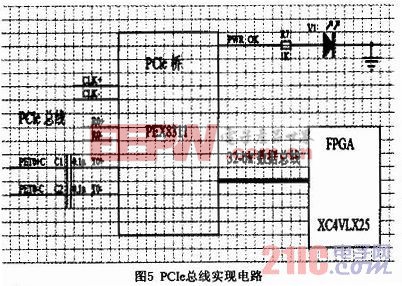

采集的视频数据经过FPGA解码处理后需要通过PCIe总线传输给嵌入式CPU以便于实时压缩存储。实现高速的PCIe总线是海量数据传输的关键。数据传输总线技术是不断更新发展的过程。在数据通讯的起初阶段,串行通讯因为信号简单、实现方便而应用广泛,占有统治地位,例如RS422串行通讯,尽管速率不高,目前仍然很有生命力。为解决串行通讯的瓶颈问题,开始采用并行传输总线,并行通讯的速率取决于时钟频率和数据宽度。目前最流行33MHz/32bit的PCI总线,峰值传输速率可达132Mbps。当继续提高时钟频率时,并行通讯总线的数据宽度却成为继续提高速率的障碍。由于极高频下的线路串扰和反馈,难以保证多路并行总线信号数据同步的一致性,数据通讯的传输技术从并行回归到串行,并行双向的PCI总线发展为串行单向的PCIe总线。速率高达2.5Gbps的PCIe总线有三对差分信号,即同步时钟CLK+/CLK-、接收信号R+/R-和发送信号T+/T-。PCIe总线设计电路如图5所示。

在PCIe这种高速信号传输总线中,数据不是直接通过信号导线的电压信号,而是通过高频耦合方式传输的。图5中的C1、C2就是发送方的耦合电容,应尽量靠近桥片。每一对差分信号都应该有耦合电容,图5中时钟和接收信号对的耦合电容,隐含在PCIe的主控方。

评论