一种面向H.264视频编码器的SoC验证平台

OR1200微处理器是整个验证平台的控制核心,根据系统的需求和节约的原则,裁去了OR1200中的指令缓存器(IC)、数据缓存器(DC)和存储器管理单元(IMMU和DMMU)。SoC平台中另一个重要的模块就是片上存储器(Onchip-Memory)。片上存储器数据访问能力强,功耗低,但是容量有限,只能实现代码量比较小的特定功能(如硬件初始化、CPU启动引导等)。当完成这些操作后处理器就会跳转到主存储器SSRAM的地址空间执行代码。

在其他的外设模块中,UART-BOOT模块只带有一个Wishbone主端口,用于控制CPU的启动和程序下载,它不需要分配地址。其他模块的地址空间分配情况如表1所列。本文引用地址:http://www.eepw.com.cn/article/165871.htm

在图1所示的IP核中,除了以下几个模块外均可从Opencores网站上免费获得:UART-BOOT模块是为了在验证过程中更加方便地更新下载软件代码和对SoC平台进行控制,需要自主设计;图像采集模块可参考友晶科技公司的参考设计,但是其采集到的数据为RGB格式,需要转换为H.264编码器所需要的YUV格式;此外,由于图像采集模块内部的MT9P031图像传感器是逐行扫描的,而H.264编码器是以宏块顺序进行编码的,因此SDRAM的控制器需要重新进行设计,以满足逐行写入和按宏块读出的要求。

之前有很多人对构建基于嵌入式软核的SoC系统作了研究,本文重点介绍与H.264编码器验证相关的自主设计的模块上。

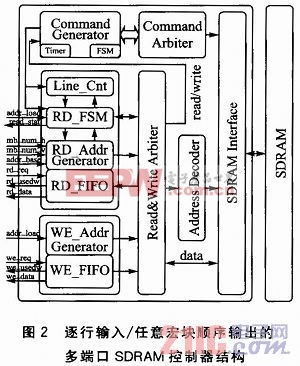

3 多端口SDRAM控制器

逐行输入/任意宏块顺序输出的多端口SDRAM控制器的整体结构如图2所示。

评论