基于NAND FLASH的大容量视频存储系统的设计

FPGA作为DSP的异步外设连接到DSP的系统总线上,DSP通过存储器DMA的方式向FPGA发送数据和读取FPGA内部RAM中的数据。考虑到FPGA自身I/O引脚数量的限制和引脚驱动能力,本系统采用两片FPGA来驱动100片FLASH,FLASH阵列分为25组,每组4片FLASH,共用一套数据/地址总线和控制总线,各片FLASH通过片选信号来选中。

DSP的PPI接口接收到的视频数据是经过MPEG-4格式压缩过的,其最大bit流速率为4 Mb/s。PPI的总线时钟频率最大可达133 MHz,也就是数据传输速率最大可达133 M×16 b/s,所以对于4 Mb/s的视频数据完全可以满足要求。视频数据到达存储板后,由FPGA负责写入存储器,存储芯片K9WBG08U1M的写入速率为5MB/s,每路视频数据率为4Mb/s=0.5MB/s,故存储芯片K9WBG08U1M也可以达到存储速率的要求。

2.3 FLASH的驱动设计

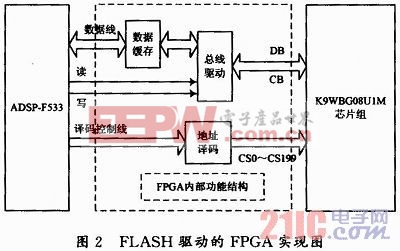

本系统采用FPGA给FLASH提供总线驱动和译码逻辑,以其中一片FPGA为例,其具体实现图如图2所示。本文引用地址:http://www.eepw.com.cn/article/165555.htm

在FPGA内部构建两个双口RAM,一个用于存储操作,一个用于下载操作。当进行存储操作时,FPGA首先接收DSP发送的数据(包含地址信息)存储在双口RAM中,此过程采用MDMA的方式。数据接收完成后,DSP给FPGA发送启动信号,此时FPGA开始产生FLASH控制时序将存储在双口RAM中的数据写入FLASH中,同时根据地址信息译码产生相应的片选信号来选中某一片FLASH芯片。在编程过程中,只要保证下一次MDMA结束前当前页编程已经结束,就可以产生一个脉冲通知DSP准备下一页写入操作,这样可以让MDMA与编程同时进行,从而提高写入速率;同理,在进行下载操作时,先将FLASH中的数据缓存到双口RAM中,然后通知DSP进行MDAM操作即可。图3给出了存储操作的功能仿真波形。从图中可以看出完全满足FLASH的写入时序,经验证,此模块实现的存储效果非常好。

评论