基于FPGA的任意波形发生器设计与研究

图6 输出波形图

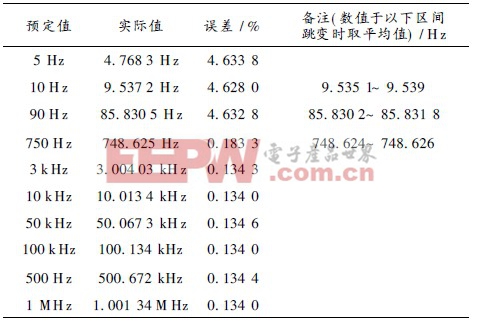

4. 2 频率测量

通过设定预定值, 用计数器测量出实际值, 基于此数据计算出误差如下表( 只选取10 组数据) 。

由表1 可看出, 1 ~ 100 Hz 区间误差较为明显,1 kHz~ 1 MHz区间输出频率较为稳定( 该表为测试正弦波数据) 。

表1 频率数据表

4. 3 误差与杂散分析

除了工作环境与电源噪声等问题是影响到频谱纯净度的因素外, 还有以下主要原因:

( 1) 相位截断产生杂散信号。硬件上无法满足20 位的数据储存, 设计中均采用了高位截断的方法, 只取用累加器输出的高几位用于查表, 低位舍去。必然会造成误差从而影响最终的输出信号频谱。正弦信号上引入了余弦分量, 造成时域上的叠加, 必然表现为频域上的杂散。

( 2) D/ A 转换器非线性引起的杂散分量。理想DAC 对DDS 的影响只表现在对信号频谱的幅度和相位产生改变, 输出上体现出滚降特性, 并不引入其它的频率成分, 而非理想的DAC 的非线性、瞬间毛刺等非理想的转换特性在输出频谱中产生了杂散。

( 3) 幅度量化产生的杂散。正弦查表内存储的波形码事一个模拟信号被均匀量化后的值。存储器的容量有限, 不可能以无限二进制数来记录正弦值, 因此出现幅度量化误差。

减小DDS 输出电压中的杂散及噪声的方法, 除了选用性能优良、工艺精湛的D/ A 转换器, 提高位数与幅度量化字长外, 还可以通过设计良好的低通滤波器, 以滤除各种杂散及带外噪声, 也可选用DDS+ PLL 频率合成技术, 以及数据压缩法, 最高压缩比可达128 1。另外可以在产生的相位字序列上加入高频抖动( Dither) , 因为相位截位误差成周期分布, 这将导致在某些频率处产生较大的毛刺, 使DDS 产生的频谱无杂波动态范围减小。通过在相位上加入抖动, 能够破坏相位误差中较明显的周期性分布, 从而使得毛刺的幅值得到减小, 增大了输出正余弦波的无杂波动态范围 。

还可以采用相位误差反馈结构, 在SCMF( 相位累加器和正余弦函数生成器) 前加入一个二阶FIR 滤波器( Finite Impulse Response, 有限冲击响应) 来滤除输出频率附近的相位误差。

5 结 语

任意波形发生器的设计是全国电子设计大赛中经典的选题之一, 任意波形发生器的设计不仅有广泛的实践应用空间, 并且对于电子科的学生动手能力的提高及学科知识的融会贯通同样具有极大的指导价值。本文寻求功能强大、操作便捷、输出参数稳定的设计效果, 并主要偏重基础, 使之更符合教科书的典型教学条件, 并对相关参数进行测量, 分析原因。关于波形发生器的设计, 仍有许多可以设计扩展的功能, 杂散的削弱仍有较多的方法值得探究。

评论