基于CPLD的清分机纸币图像采集系统

总使能信号IMAGE_EN是N2信号经滤波、延时后得到的,它和码盘分频信号SP拓宽后的信号SP_1728逻辑相与后得到行采样使能信号SAMPLE_EN,用于控制采样间隔。这里SP是将码盘输出信号MCLK经DIV_6六分频,再经单稳态电路DIFF得到的分频数可根据实际参数(码盘刻线精度、电机转速)修改。DIFF可以将前面的分频信号变为脉宽为1个时钟周期的脉冲信号,其内部标识状态为Q1Q0。当输入脉冲Sin为低电平时,Q1Q0=00,输出脉冲Sout=0;Sin为高电平时,Q1Q0=00,表明Sin的上升沿出现在前一个时钟周期,Sin=1,并Q1Q0=11;若Q1Q0≠00,则表明Sin的上升沿并非刚到达,Sout清零,Q1Q0=10。

信号SP_1728的脉宽为1 728个移位时钟周期,确保在每一行采样的过程中,全部且仅将1 728个点的图像信息输出。内部RAM的写地址端接人一个12位加法计数器ADDRESS_12b,对ADRO_CLK计数,输出RAM的12位写地址,清零端接CIS SV233A4W的启动信号SP。

4仿真与结果分析

4.1时序控制仿真

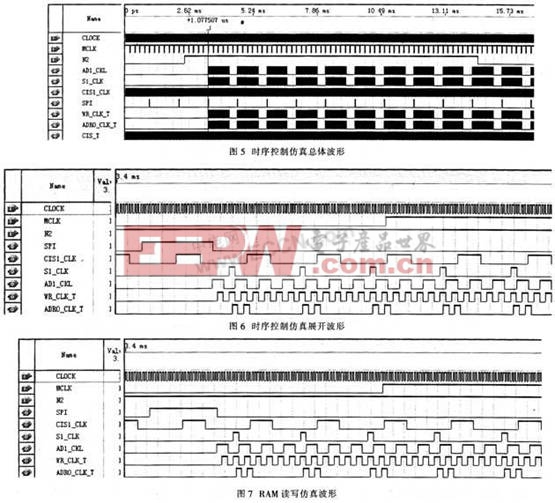

按照系统设计结构,该系统输入时钟CLOCK的频率为50 MHz,码盘信号频率为6 kHz,其仿真波形如图5和图6所示。由仿真波形可看出,满足系统要求中时序关系,由于A/D转换器只有一路输入,所以每3个输出数据有一组数据为有效地址。

4.2 RAM读写仿真

存储在CPLD内部RAM的采样数据要由后续DSP处理模块读取。在写时钟wrclock的作用下,从地址0开始向RAM依次写入0、1、2、3……,然后在RAM的读时钟端施加一个读时钟rdclock,在读地址rdaddress端施加从0递增的读地址,仿真RAM的读写,得到的仿真波形如图7所示。由仿真波形可以看出,RAM的读写正确,读取的数据相对于读时钟有一定延时。

5结语

该高速图像采集装置已在钞票清分机中得到良好应用。该系统设计也可应用于连续、高速的图像采集系统,另外,还可采用接触式传感器,使其具有曝光时间短,感光速度和数据传输速度快,实现高效输入等特点,从而能够很好的满足清分机对采样图像质量的要求。

评论