基于Stratix III的DDR3 SDRAM控制器设计

3.1 ALTMEMPHY设计

ALTMEMPHY是可配置参数的宏功能,用户可根据设计需要配置相应参数[3]。ALTMEMPHY主要 包括时钟与复位管理、地址与指令通路、读数据通路、写数据通路、自校准等组成模块。

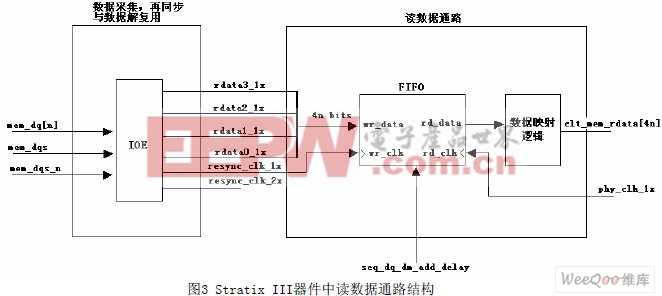

时钟与复位管理模块主要负责时钟信号的产生与移相,以及时钟网络类型的控制;地址与 指令通路负责接收控制器输出的地址和指令信号,并将其从半速率时钟转换为全速率时钟;读 数据通路是采集从存储器读出的数据,并将其再同步到系统时钟域;写数据通路将控制器输出 的半速率数据转换为双倍速率(DDR)信号,以写入DDR3器件;自校准模块用于系统上电时自动 校准DDR3器件的过程变量,以获得最大的时序余量,消除来自读数据通路的不确定因素,提高 系统高频工作下的稳定性。图3所为Stratix III器件中读数据通路的结构框图,由图中可以看 出DDR与HDR转换的过程中数据总线宽度及时钟频率的变化。

用户自定义控制器部分主要由以下模块组成:主控模块、地址与指令译码、数据缓冲、时 钟同步、初始化与刷新请求等[4]。 主控模块主要由有限状态机实现,完成系统从上电开始所有状态间的转换、任务调度、总 线仲裁、时序同步等,并对其他模块产生相应的控制信号,协调各模块工作;地址与指令译码 模块在主控模块的控制下,完成对系统各种访问指令和访问地址的解码与匹配;数据缓冲负责 在与ALTMEMPHY进行数据传输过程中对数据进行FIFO缓冲和同步;时钟同步模块采用了PLL锁相 环电路设计,为ALTMEMPHY提供参考时钟,同时接收ALTMEMPHY输出的同步时钟phy_clk作为系统 时钟,完成各模块之间的同步;初始化与刷新请求模块完成SDRAM器件的初始化及自刷新操作。

3.3 设计注意事项

本系统工作频率高,任何微小的时序错误都可能导致系统不能正确工作。虽然ALTMEMPHY 结构可以在一定程度上减小时序错误,但在设计过程中仍要做好代码的优化,尽量采用同步电 路设计方法,消除竞争冒险现象,保证数据接口的同步等。

另外,在设计中要遵照Altera提供的设计规范进行设计,如时钟信号要从片上PLL专用的全 局时钟引脚输入以减小时钟倾斜;各种时钟分别配置于各自独立的时钟局域网络内以避免相位 搅动;对周期、建立、保持时间等关键参数添加相应的约束等等,以提高设计的工作频率,增 强系统的稳定性。

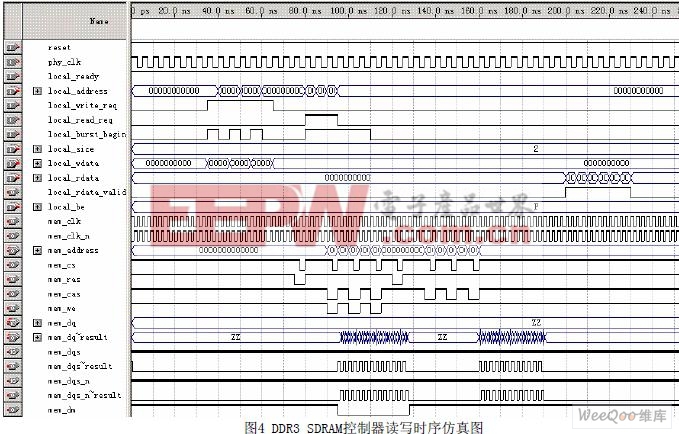

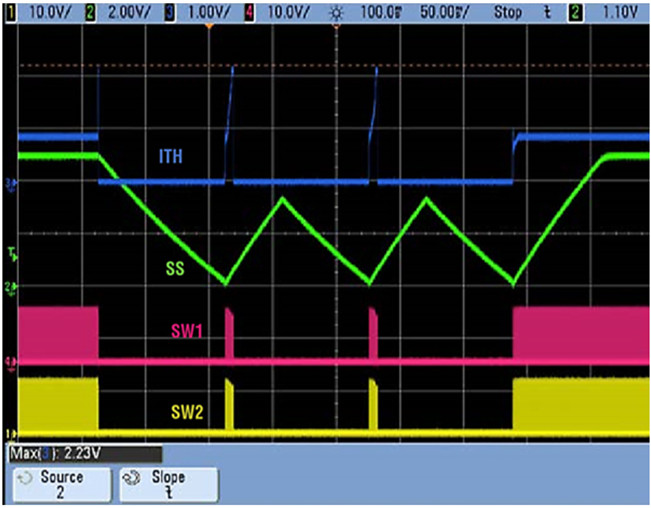

设计采用的FPGA为Stratix III系列中的EP3SL150F1152-C2。Stratix III是Altera公司刚刚面市高端FPGA系列,也是目前少数支持DDR3接口的FPGA之一。Stratix III系列提供读写均衡、 DQ去斜移I/O延时、动态片内匹配等功能,并且使用可配置锁相环(PLL)来补偿电压和温度变化, 以充分发挥DDR3存储器的优势。Stratix III器件支持最大时钟速率400 MHz、最大数据速率800 Mbps的DDR3[5]。软件设计在Altera公司的Quartus II 7.2平台上,运用自顶向下的设计思想, 采用VHDL语言加电路图混合设计的方法完成。测试读写仿真时序如图4所示。

本设计采用Samsung公司的1Gb容量DDR3 SDRAM芯片K4B1G0846C-ZCF7予以实现。该芯片组织 结构为16Mbit x 8 I/Os x 8banks,速率为800Mbps。通过仿真和工作实测,系统稳定工作频率 达到400MHz,8位数据总线带宽最大传输率达到800MB/s[6]。 从设计的仿真及实现结果可以看出,这种结构的控制器具有很高的传输速度和稳定的性能 表现,可以作为下一代存储设备广泛运用于各种高速高性能系统设计中。同时,该设计为相关 控制器的开发和研制提供了实例,具有良好的参考和应用价值。

本文作者创新点:提出了一种基于Stratix III的DDR3 SDRAM控制器的设计方法,采用 ALTMEMPHY宏功能结合自定义控制器的结构,即保证了系统在高速运行时的稳定性,又可以根据 用户需要灵活改变参数设置,可广泛应用于各种相关高速数字系统。

评论