数字接口系列文章之SPI总线

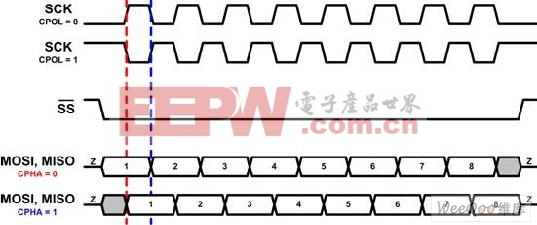

除设置时钟频率之外,主节点还会配置相对于数据的时钟极性和时钟相位。这两个选项分别称作 CPOL 和 CPHA,能够允许时钟信号实现 180 度相移且数据延迟半个时钟周期。图 3 显示了相应的时序图。

图 3 时钟极性和相位的时序图

CPOL = 0 时,时钟在逻辑 0 处空闲:

*如果 CPHA = 0,数据会在 SCK 的上升沿上读取,在下降沿上变化。

*如果 CPHA = 1,数据会在 SCK 的下降沿上读取,在上升沿上变化。

CPOL = 1时,时钟在逻辑高电平处空闲:

*如果 CPHA = 0,数据会在 SCK的下降沿上读取,在上升沿上变化。

*如果 CPHA = 1,数据会在 SCK 的上升沿上读取,在下降沿上变化。

在 SPI 中,主节点可以与单个或多个从节点进行通信。在使用单个从节点的情况下,从选择信号可以关联到从设备的本地接地电位以允许永久接入。对于使用多个从节点的应用,可能有两种结构:独立和菊花链式从节点(请参见图 4)。

图 4 主节点与独立从节点(左)以及菊花链式从节点(右)进行通信

从节点独立寻址时,主节点必须提供多个从选择信号。该结构一般用在数据采集系统中,其中的多个模数转换器 (ADC) 和数模转换器 (DAC) 都必须单独接入。

菊花链式从节点需要主节点提供唯一的从选择信号,因此该结构要求同时启用所有从节点,以确保菊花链内通过所有移位寄存器的数据流不会中断。典型的应用为工业级 I/O 模块中的级联多通道输入串行器和输出驱动器。

评论