基于VHDL/CPLD的I2C串行总线控制器设计及实现

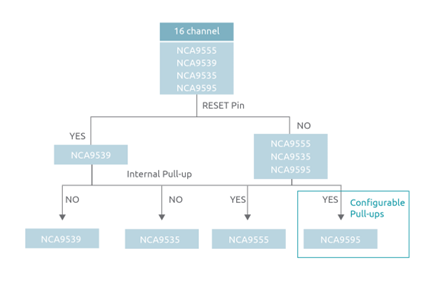

I2C(Inter IC BUS)是Philips公司开发的用于芯片之间连接的总线。 I2C总线用两根信号线进行数据传输,一根为串行数据线(SDA),另一根为串行时钟线(SCL)。I2C总线允许若干兼容器件(如存储器、A/D转换器、D/A转换器、LCD驱动器等)共享总线。I2C总线理论上可以允许的最大设备数,是以总线上所有器件的总电容(其中包括连线本身的电容和连接端的引出电容)不超过400pF为限,总线上所有器件依靠SDA线发送的地址信号寻址,不需要片选线。任何时刻总线只能由一个主器件控制,各从器件在总线空闲时启动数据传输。I2C总线数据传输的标准模式速率为100kbps,快速模式速率为400kbps,高速模式速率为3.4Mbps。

本文引用地址:http://www.eepw.com.cn/article/163062.htm用VHDL和CPLD设计数字系统具有传统方法无可比拟的优越性,它已经成为大规模集成电路设计最为有效的一种手段。为简单起见,本文采用VHDL设计标准模式的I2C总线控制电路。

1 I2C总线上的数据传输

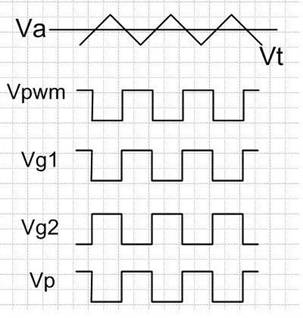

I2C总线包含时钟线SCL和数据线SDA两条连线,SCL由主机产生。I2C总线的数据传输流程如图1所示。其传输过程为:首先主机产生起始位,然后传送第一个字节。8位数据中首先传送的是数据的最高位MSB,最低位LSB为读写指示位,1表示主机读,0表示主机写,高7位地址可使主机寻址128个从器件。

从机收到第一字节数据后发响应位,主机收到响应位后接着发送第二个字节的数据。数据发送完毕后产生结束位,数据传送结束。数据传送时,只有时钟SCL为低电平时SDA才允许切换,SCL为高电平时SDA必须稳定,此时SDA的电平就是总线转送的数值。

在SCL为高电平时,SDA线由高到低切换表示起始位,SDA线由低到高切换表示停止位。起始位和停止位由主机产生,在起始位产生后总线处于忙状态,停止位出现并经过一定时间后总线进入空闲状态。发送器每发送一个字节后,接收器必须产生一个响应位。响应位的驱动时钟由主机产生则接收器将SDA线拉低产生响应位。如果主机是接收器,则接收最后一个字节时,响应位为1,通知从机结束发送,否则响应位为0。当从机不能响应从机地址(例如它正在执行一些实时函数,不能接收或发送)时,或响应了从机地址但在传输一段时间后不能接收更多的数据字节,此时从机可以通过响应位为1通知主机终止当前的传输,于是主机产生一个停止位终止传输,或者产生重复开始位开始新的传输。

SDA线上传送的数据必须为8位,每次传送可以发送的字节数量不受限制。如果从机要完成一些其他功能(例如执行一个内部中断服务程序)才能接收或发送下一个数据字节,则从机可以使SCL维持低电位,迫使主机进入等待状态。从机准备好接收或发送下一个数据字节时,释放SCL,数据传输继续。

SDA和SCL都是双向线路,使用时通过上拉电阻连接到电源。总线空闲时这两条线路都是高电平,连接到总线的器件的输出级必须是漏极开路或集电极开路,这样总线才能执行“线与”的功能。

评论