基于VerilogHDL的CMOS图像敏感器驱动电路设计

3 Verilog HDL驱动时序设计

经过以上分析可知,CMOS图像敏感器采集时可以分为RESET过程和采集过程。时间上两个过程是独立的,如图3。但在FPGA内部处理这两部分的电路物理上是同时存在,因此必须将相应的信号通过置标志位的方法置为有效或无效。

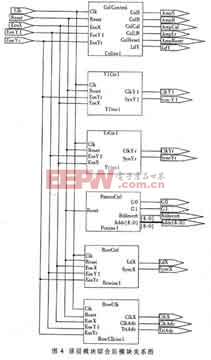

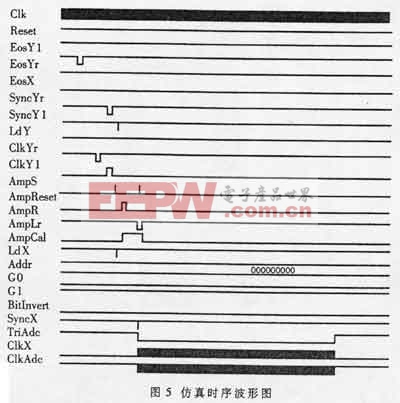

STAR250所需数字驱动信号共28个,其中SELECT信号在正常使用时,直接接PCB板的Vcc。因此需FPGA控制的驱动信号有27个。根据采集过程可以把信号划分为列放大器信号,包括CAL、Reset、Lr、S、R、LdY。这6个信号在每一行的初始化部分都要用到,因此可以编写到一个模块(ColControl)中;模式信号(PaternCtrl)模块用来设置CMOS敏感器的工作模式及初始地址,包括G0、G1、Bitlnvert和Addr[8:0]共12个信号。其中G0、G1用来设计输出的放大倍数,BitInvert用于将输出取反,Addr[8:0]则设置采集的起始地址;行读出信号控制模块(YlCtrl)产生行读出地址的同步信号SyncYl及时钟驱动信号ClkYl;行RESET信号控制模块(YrCtrl)产生行RE-SET地址的同步信号SyncYr及时钟驱动信号ClkYr;像素控制模块(RowCtrl)产生行内像素初始地址的装载信号LdX及同步信号SyncX;行内时钟信号模块(RowClk)产生列内像素的时钟驱动CLKX、ADC驱动时钟信号CLkAdc及输出三态控制信号TriAdc。系统的输入信号为主时钟CLK、EosX行内像素结尾信号、EosYl帧内行结尾信号、EosYr帧内RESET行结尾信号、芯片的RESET信号。经过这样划分后的模块化Verilog程序就比较易写了。经过顶层模块综合生成的网表如图4。布线仿真时序图如图5,其中时钟信号过于密集变成黑色带状,同样输出时钟CIkX及ClkAdc也是黑色带状。在时序上ClkX与ClkAdc是反相关系,在TriAdc保持低电平时输出有效。所设计的驱动信号仿真波形与理论波形十分符合。这样就完成了STAR250的时序驱动电路设计。

使用Verilog语言设计时序逻辑具有很高的效率。结合CMOS敏感器特性可以方便地开发出驱动时序电路。但必须对CMOS图像敏感器的信号分析准确,正确分离那些独立的信号和共用的信号,用时序逻辑设计驱动信号,用组合逻辑实现不同采集过程时间上的分离。布线延迟是必须考虑的,采用流水线技术可以预测延迟,保证信号的正确性。虽然文中并未给出像素ADC输出的存储电路,但实际上直接使用TriAdc信号作为SRAM的片选,ClaAdc的低电平作为写信号,SRAM的地址在ClkAdc的上升沿增加、下降沿写入。这样就可以完成图像数据的存储。以上Verilog程序在FLEXl0kl0上布线实现。经示波器观察逻辑正确,CMOS敏感器正常工作。

评论