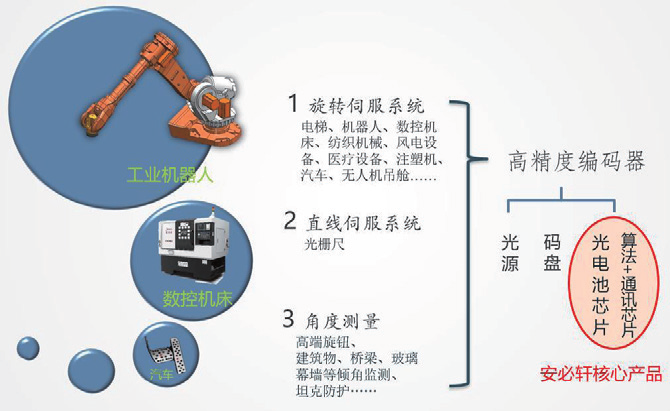

基于绝对编码器的数据采集

3 接口的设计及编程

编码器要求时钟发生电路提供的时钟信号可以调整,调整范围为100 kHz~1 MHz。根据逻辑时序的要求,在静止条件下,时钟和数据信号处于逻辑高电平上,编码器内部单稳态电路不工作。在第一个时钟信号下降沿,单稳态电路启动,编码器内部的并行数据信号输入到P/S(并/串)转换器,并在转换器内存储。在时钟信号上升沿MSB(最高有效位)被传送至输出端的数据线上。当时钟信号再次至下降沿,接口从数据线上得到MSB数据,当数据稳定后,单稳态电路再次重新启动。每次当顺序时钟脉冲信号在上升沿时,数据连续传送至输出数据线上,同时需要控制信号处于下降沿。在顺序时钟脉冲结束时,外部控制信号时钟需要获得LSB(最低有效位)的数据,当顺序时钟脉冲被中断,单稳态电路不再启动。一旦TM(单位定时电路时间信号)消失,数据线路回到逻辑高电平上,编码器内部单稳态电路自动停止工作。信号波形示意如图2所示。本文引用地址:http://www.eepw.com.cn/article/162261.htm

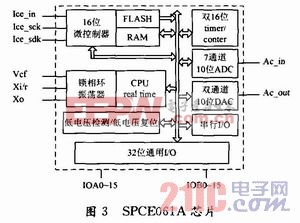

为了产生时钟信号,选用SPCE061A芯片作为处理器,该芯片为16位芯片,带32位I/O,具有串行输出接口,双16位定时器/计数器,内部结构如图3所示。

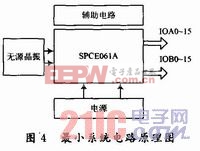

以SPCE061A芯片为处理器,设计一个最小系统,如图4所示。

评论