单片机+CPLD的多路精确延时控制系统

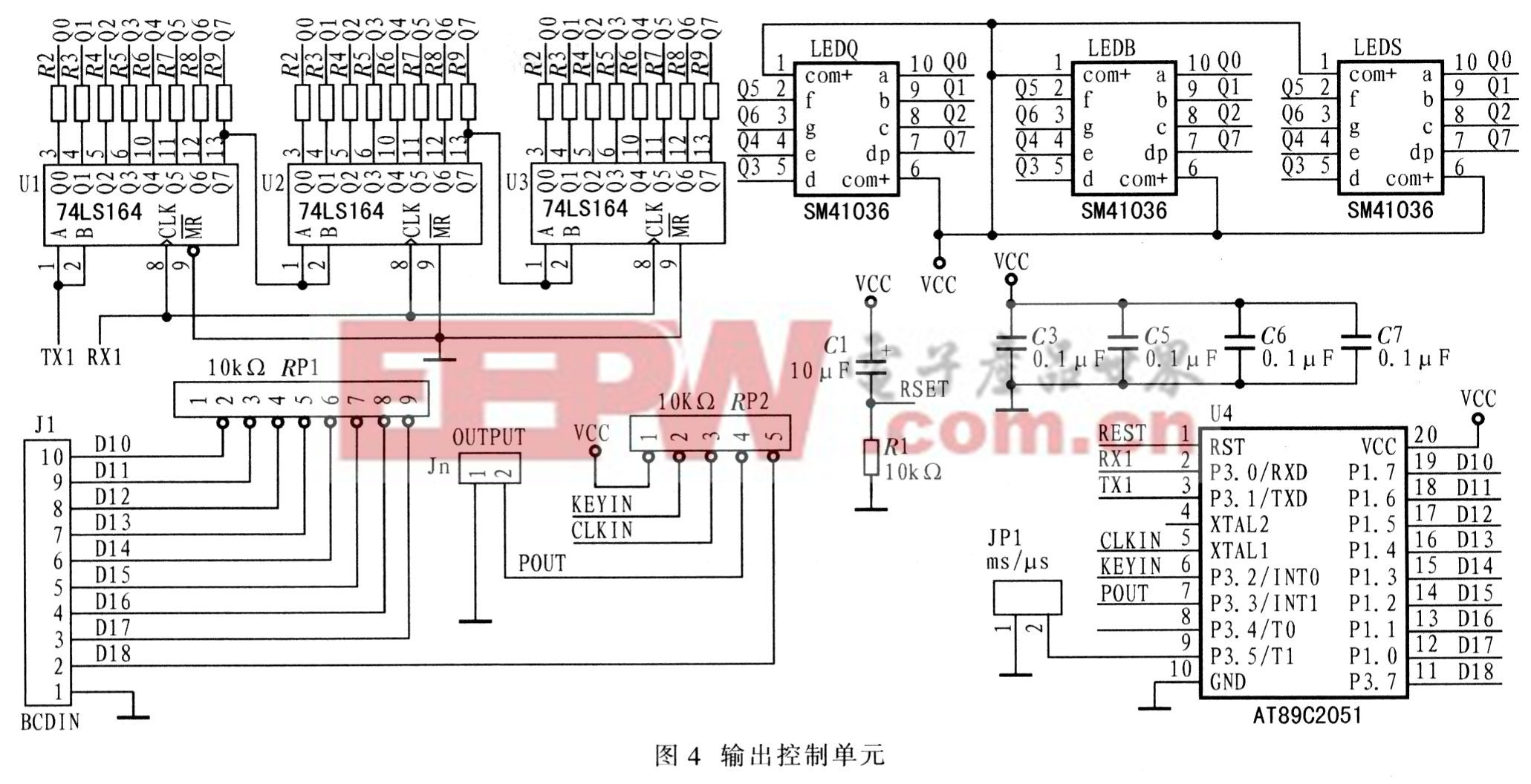

每个系统由n(本系统设计中n=9)个输出控制单元组成,这n个单元输出控制独立并行工作,如图4所示。N0.1~N0.n以ATMEL公司5l系列单片机AT89C2051为核心。AT89C205l是低功耗、高性能CMOS 8位单片机,具有15个双向输入/输出(I/O)端口、片内含2 K字节的可反复擦写的只读Flash程序存储器和128字节的随机存取数据存储器(RAM);采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS一5l指令系统。输出控制单元(NO.1~NO.n)并行工作,完成延时时间设置、μs/ms变换设置、控制信号输出和延时显示等功能,延时时间显示通过单片机串口实现,由3片串/并变换器件74LSl64驱动3个共阳数码管。本文引用地址:http://www.eepw.com.cn/article/162113.htm

4 系统软件设计

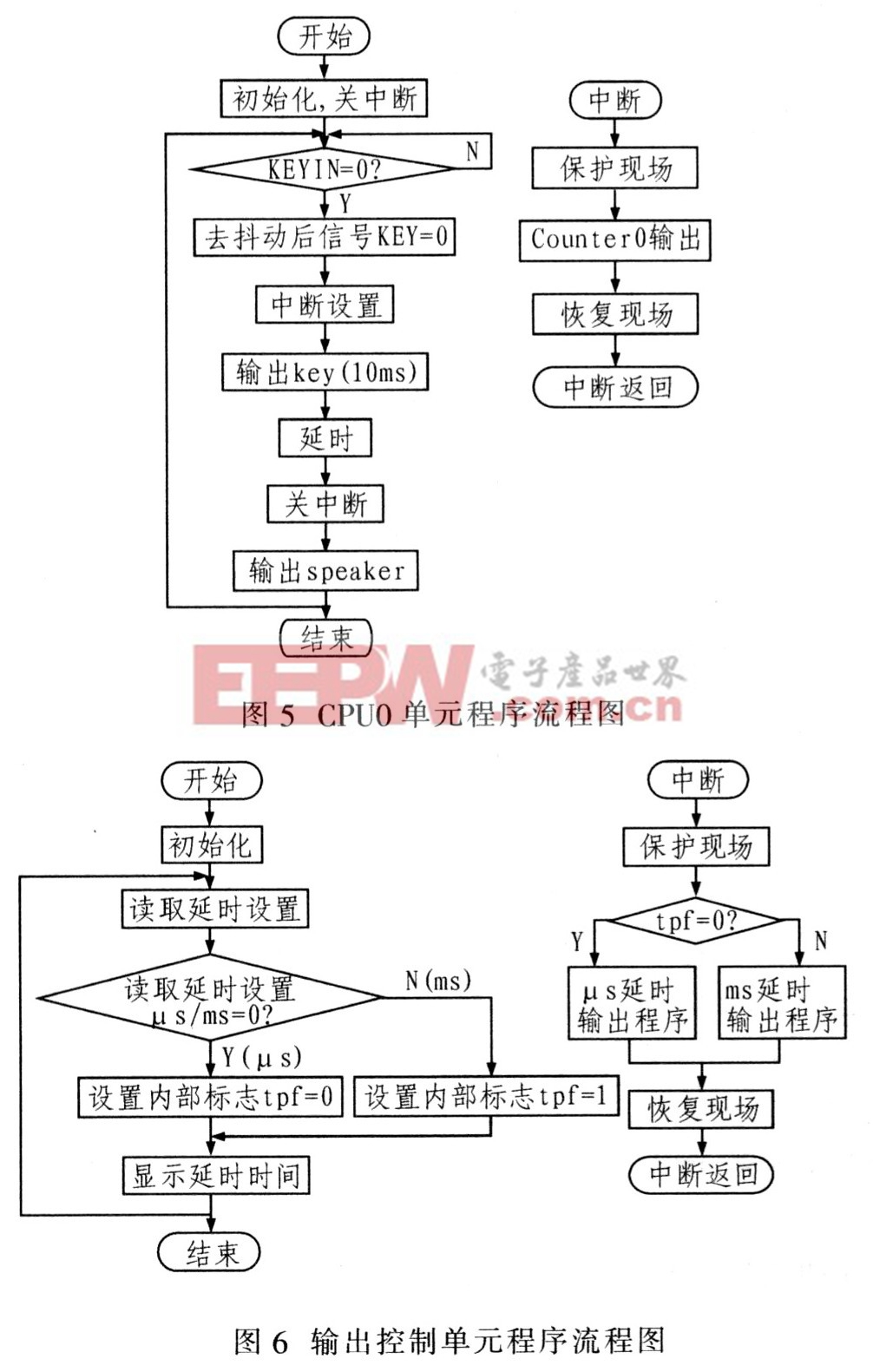

本系统软件设计包括CPUO单元、NO.1~NO.n输出单元及CPLD单元程序设计。由于对时间要求严格,采用汇编语言编写,信号输出由中断程序完成,由于中断响应过程、现场保护以及中断后必要的设置条件检测需要时间,所以软件必须通过容余指令(比如NOP)的延时,可保证counter0输出和控制信号延时起点在同一时刻。

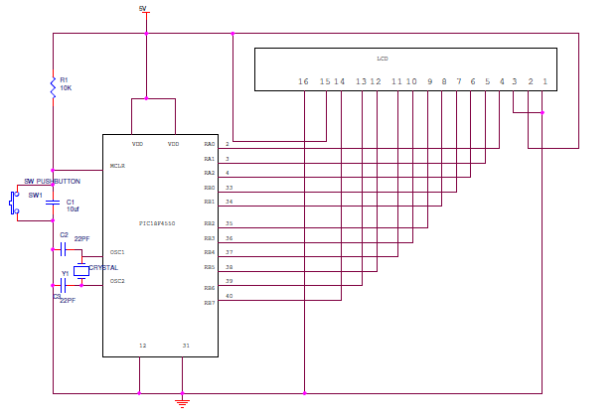

CPU0单元程序流程如图5所示。CPU0主程序完成系统初始化、按键检测、去抖动信号输出和工作状态提示音输出等工作,中断服务程序计时基准信号counterO输出。输出控制单元NO.1一NO.n程序流程如图6所示,各单元主程序完成μs/ms设置检测,延时设置读取,延时时间显示,中断程序完成控制信号输出功能。CPLD程序采用VHDL语言编写,采用QHalftusⅡ软件编译仿真。

5 结语

该系统设计可应用于电容组(9只)放电控制系统,在放电电子开关控制端、

评论