赛灵思System Generator中的时间参数

在第二类时间参数,即分析参数中,首先要考虑的是采样时间(ST)模块。该参数在系统实施中不使用硬件资源,仅用于Simulink模型中的分析目的。ST模块显示的tsam值指的是硬件实施中用于相关信号的时钟启用周期,其单位是FPGA时钟周期。

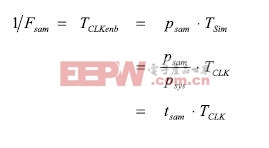

当设计人员在System Genertaor中的Icon Display属性框中选择下一项分析参数,即采样频率时,该模型中的每个Xilinx模块都会以MHz为单位显示采样频率Fsam,并用于该单元的实施。采样率与其它时间参数的关系如下:

其中TCLKenb是实施中启用的相关时钟的周期。

从上面的第二个等式可以清楚地看出,每个采样周期Psam都必须是Simulink系统周期Psys的整数倍,之所以如此,是因为仅有这些时钟启用信号是从FPGA系统时钟衍生出来的。第三个等式表明ST时钟显示的值是以FPGA时钟周期为单位的时钟启用周期。

选择时间参数的详细指南

上述控制系统示例详细说明了如何选择时间变量,该流程具体可分为以下五个步骤。

确定设备

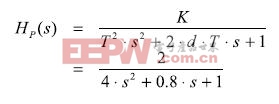

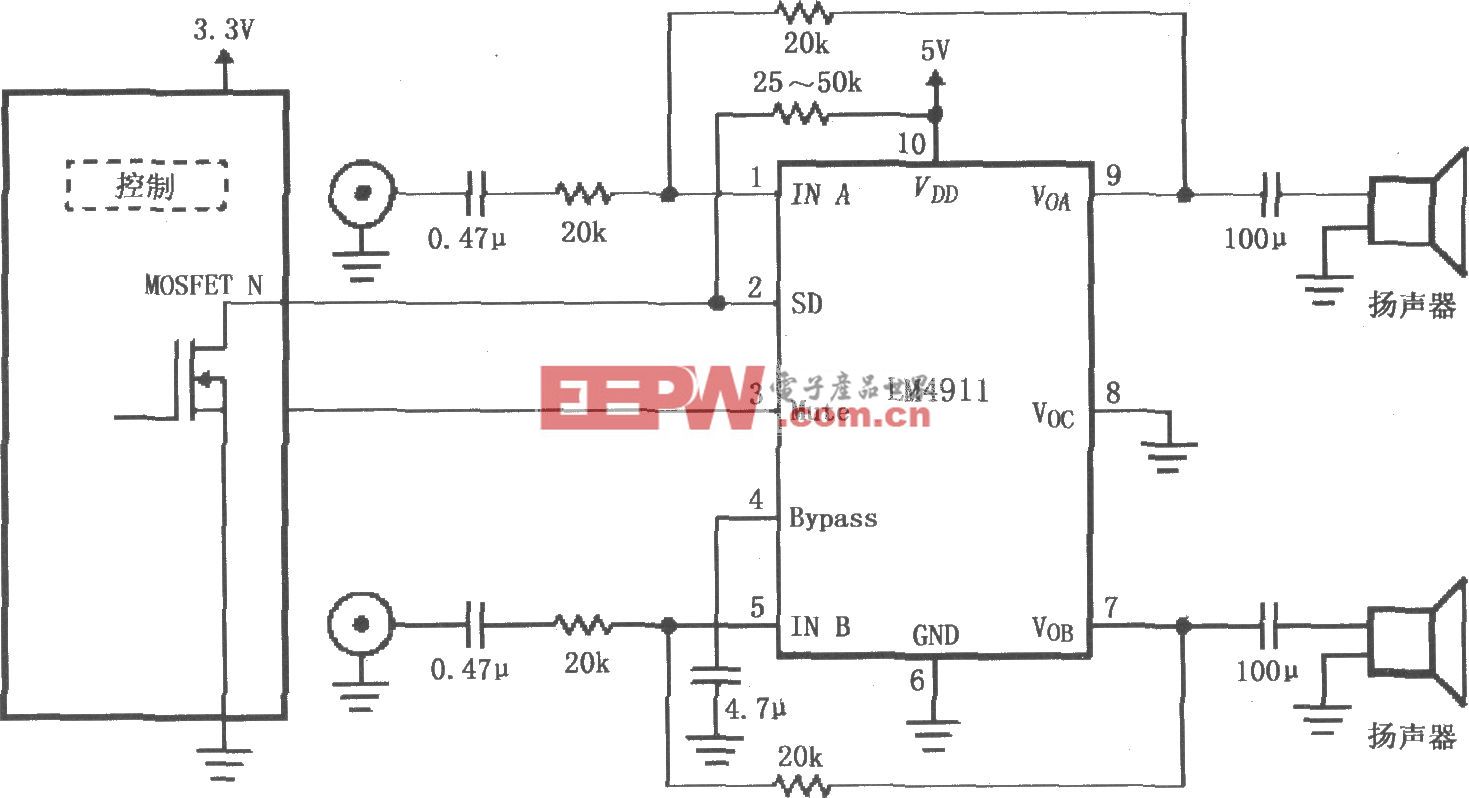

采用合适的传递函数对设备建模。在本例中,将设备当作PT2元进行建模,将增益系数K设定为2,时间常数T设定为20ms,衰减系数d设定为0.2。因此,如图3(a)所示,该设备为一个振荡元。

图3在无控、有PID控制和无抗饱合以及有抗饱和的情况下,输入命令后得到的整体系统模型(顶部)和设备输出

选择模拟时间单位

此时,可以选择基础模拟时间单位Tsim,这样设备的传递函数就有了便利的数值参数。在本例中,将Tsim设定为10ms。在上述参数设定完毕后,便得到如下设备传递函数:

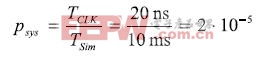

设置Simulink系统周期

在拥有模拟时间单位后,将随之根据可用的硬件平台FPGA时钟周期TCLK设置Simulink系统周期Psys。在Spartan-3E入门套件中,系统时钟频率为50MHz,设定TCLK为20ns,得到:

确定采样频率

根据经验法则,数字控制器的采样率必须至少是设备截止频率的20倍。本示例设备的截止频率大约是30Hz,因此将采样频率设定为Fsam=1kHz。

设定采样周期

最后,在控制器前面的Gateway-In模块中设定采样周期参数Psam。在本例中,设置如下:

有了这些设置,就可以进行模型模拟,调整控制器参数并合成控制器逻辑。不过,有时FPGA时钟周期TCLK会显著小于基础时间单位Tsim,如在控制器是一个时钟频率比控制器本身要求高很多的更大规模设计的一个组成部分时。如此一来,由于在控制器真正处理下一个数据样本之前需要模拟大量无效的时钟周期,模拟时间会变得无比漫长。而这种情况下,可以在不影响设备一致性的同时,在模拟和实施中设置不同的Psys。之所以能这样做,是因为Psys值仅对设备的 System Generator部分有所影响。

更具体地说,可以在模拟控制系统时设置Psys=Psam。这样可确保只在必要时,即只有在模块真正改变状态的时候才会调用System Generator模块。在生成FPGA实施前,只需改回原来的Psys值即可。

结语

闭环控制系统的MBD要求设备传递函数的绝对时间测量指标与设计环境的时间参数保持一致。通过使用为DSP提供的Xilinx System Generator工具,本文为该问题提供了一个系统化的解决方法。

评论