M4K块移位寄存器数据读进方式的逻辑分析仪设计

4 VGA显示界面的设计

VGA界面设计主要完成对结果的显示。可以对测试对象的数目、采样模式、触发信号的模式、采样频率进行控制,并且将结果显示成为波形图以便使用者进行观察。在设计中需要的字符是通过取模软件PCtoLCD2002,把定义的字模数据存储在FPGA的M4K块生成的ROM里,显示的时候从ROM读数据进行显示。

5 FPGA仿真及调试

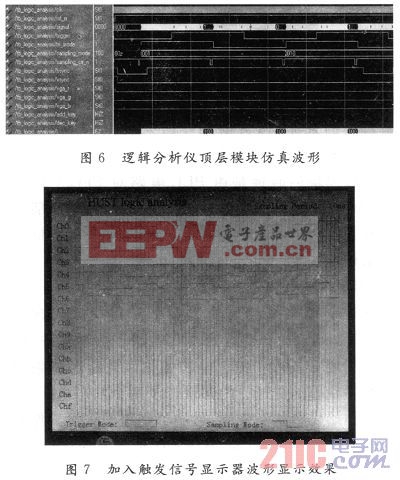

实时数据采集分析数据量大,时序复杂,以10 kHz~100 MHz的采样频率进行数据传输时,使用QuartusⅡ自带的仿真工具生成的激励,花费的时间长,而且与实际处理结果有一定的偏差,无法有效的验证整体模块的功能,同时也赡以对其进行实时模拟。本文在使用QuartusⅡ自带仿真工具的基础上,将综合后得到的结果导入Modesim 6.0中,编写Testbench提供仿真激励对逻辑分析仪的顶层模块进行仿真。通过比较整体功能进行验证。图6为逻辑分析仪顶层模块仿真波形。本文引用地址:http://www.eepw.com.cn/article/161310.htm

由图6看出,3种采样模式分别为001,010,100。001采样模式被触发后显示后64个采样数据;010采样模式触发后显示前32个采样数据和后32个采样数据;100采样模式触发后显示前64个采样数据。清除采样信号低有效,开始一个新的采样触发。经过调试,该逻辑分析仪采样频率为100 MHz。在输入采样信号的情况下,能够得到比较不错的波形。图7是在该采样频率下观察到的波形。

6 结语

结果表明,该逻辑分析仪以每8个像素为单元作为一个采样数据的显示长度,最多16路信号捕获输入通道,1路信号触发通道,3种信号采样模式,数据的分析范围和质量得到提高,可方便科研、教学使用。

评论