可编程逻辑技术在数字信号处理系统中的应用

在上面的VHDL描述中,ADDER4B是一个4位二进制加法器,其VHDL描述是:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ADDER4B IS

PORT (CIN4 :IN STD_LOGIC;

A4 :IN STD_LOGIC_VECTOR(3 DOWNTO 0);

B4:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

S4:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT4:OUT STD_LOGIC;

EAND ADDER4B;

ARCHITEC_TURE behav OF ADDER4B IS

SIGNAL SINT :STD_LOGIC_VECTOR(4 DOWNTO 0);

SIGNAL AA,BB:STD_LOGIC_VECTOR(4 DOWNTO 0);

BEGIN

AA=‘0’A4;

BB=‘0’B4;

SINT=AA+BB+CIN4;

S4=SINT(3 DOWNTO 0);

COUT4=SINT(4);

END behav;

4 结束语

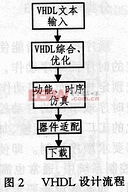

本文采用基于EDA技术的自上而下的系统设计方法,其设计流程如图2所示。该乘法器的最大优点是节省芯片资源,其运算速度取决于输入的时钟频率。如若时钟频率为100MHz,则每个运算周期仅需80ns,因而具有一定的实用价值。

评论