FlexRay的通信控制器媒体接入控制设计

引言

当前广泛应用的车载总线技术(如CAN、VAN、LIN等总线)由于缺少确定性、同步性及容错机制等并不能满足要求,FlexRay联盟推进了FlexRay的标准化,使之成为了新一代汽车内部网络通信协议。FlexRay关注的是当今汽车行业的一些核心需求,包括更快的数据速率、更灵活的数据通信、更全面的拓扑选择和容错运算。

FlexRay总线中的每个接入端称为节点。节点主要由电源供给系统(Power Supply)、总线驱动器(Bus Driver)、固化有FlexRay通信协议的通信控制器(Communication Controller)及主机(Host)4个部分组成。通信控制器是通信节点的核心器件。它主要的功能有媒体接入控制、时钟同步、编解码、协议操作控制等。媒体接入控制功能是通信控制器的核心功能,解决数据进入FlexRay通信控制器的方式,为通信控制器的编解码功能做好时间准备以及数据准备。

本文提出一种FlexRay通信控制器媒体接入控制的设计方法。该方法直接访问内存,大大缩短了获取配置的时间;设计更加精简,能够保证通信的稳定性。

1 媒体接入控制的设计

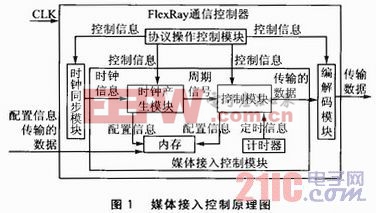

本文提出的基于内存方式实现媒体接入控制的方法包括以下步骤:首先,媒体接入控制模块的所有子模块在统一时钟域下工作,用户把与媒体接入控制相关的配置信息写入内存;然后,媒体接入控制的各个子模块直接从内存中读取该信息。媒体接入控制原理图如图1所示。

时钟产生模块根据用户的配置信息,对控制器晶振产生的最小时钟节拍按照协议规定形成系统所需要的时钟周期;控制模块根据用户配置的信息将时钟周期进一步划分为4个独立的段,即静态段、动态段、符号窗口、网络空闲段;计时器模块根据用户配置信息实现计时功能,用来记录媒体接入控制所需要的时间。

1.1 时钟产生模块

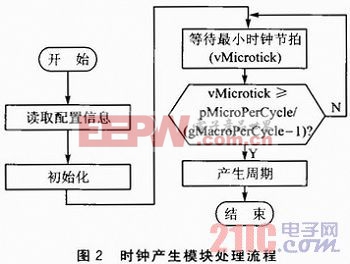

时钟产生模块实现媒体接入控制所需要的时钟周期,为编解码功能做好时间准备,同时把该信息传递给控制模块。该模块首先从内存中读取所需配置信息,主要有gMacroPerCycle、gdStaticSlot、pMicroPerCycle。时钟产生模块根据这些配置信息进行初始化操作,然后等待晶振的最小时钟节拍(vMicrotick)。当最小时钟节拍大于等于pMicroPerCycle/(gMacroPerCyclc-1)时,该模块产生周期。

时钟产生模块处理流程如图2所示。

1.2 控制模块

控制模块主要为FlexRay通信控制器的媒体接入控制功能提供所需的时隙划分,主要有静态段(static segment)、动态段(dynamic seg ment)、符号窗口(symbol window)、网络空闲段(network idle time)。

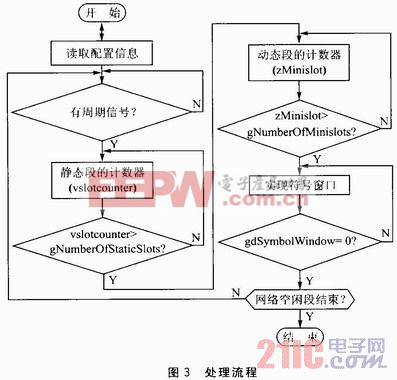

本文提出的基于内存的方式实现控制功能的思路如下:首先从内存中读取所需要的配置信息,主要有gdstaticSloc、gNumberOfMinislo ts、gdSymbolWindow、gdActionPointOffset、gdMinislotActionPointOffset。当接收到时钟产生模块提供的周期开始信号时,控制模块根据gdstaticSloc实现周期中的静态段。静态段使用静态槽实现TDMA,以协调数据的传输。在每个通道,通信控制器上设置一个槽计数器(vslotcountcr),统计静态槽的个数。当时钟周期开始的时候,设置槽计数器的值为1;当槽结束的时候,槽计数器的值加1。对于一个具体的簇,静态槽的总数是一定的,由参数gNumberOfStaticSlots确定。对于每个静态槽,FlexRay通信控制器根据用户的配置和MAC模块当前的操作模式决定是否为编解码模块提供数据。

根据gNumberOfMinislots,该模块实现周期中的动态段。动态段使用动态槽实现事件触发的媒体接入方法,以协调数据的发送。通信控制器在每个通道上设置一个动态槽计数器,统计动态槽的个数。每个动态槽根据zMinislot来计数,当有数据传送时,动态槽可能占用多个zMinislot;当没有数据传送时,动态槽占用一个zMinislot。所以动态槽的大小是根据是否有数据发送决定的。对于一个具体的簇,zMinisl ot的总数是一定的,由参数gNimberOfMinislots确定;最后它根据gdSymbolWindow实现周期中的符号窗口。最后一个周期中剩下的时间就是网络空闲段。

具体处理流程如图3所示。

2 设计验证

确保设计正确性的关键是设计验证,主要通过逻辑功能仿真。逻辑功能仿真是在不考虑信号延迟的情况下对设计的逻辑功能进行验证。验证过程是:首先编写好设计的HDL代码;然后编写对应的TestBcnch,对设计进行关键性的验证;最后利用仿真软件ModelSim进行模拟,查看波形或者输出,若发现错误则查找错误原因、修改代码或者测试文件,直到符合设计要求。

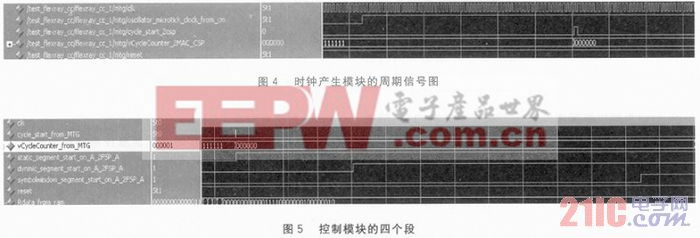

设计验证的首要工作是根据FlexRay协议设定具体的参数。具体参数的设定如下:gMacroPcrCycle=48,gdStaticSlot=4,pMicroPerCyc le=672,gNumberOfMinislots=15,gdSymbolWindow=3,gdActionPointOffsct=1,gdMinislotActionPointOffset=1。

图4是时钟产生模块的周期信号图。从图中可以看到,时钟产生模块需要等待晶振的最小时钟节拍信号,然后进行判断产生周期信号。当周期信号开始时,周期编号从默认的63变为0,然后一直编号下去直到63。

图5是对图4产生的周期信号开始周期的四个段的划分。从图中可以看到,0周期分为静态段、动态段、符号窗口、网络空闲段。

图6是静态段的媒体接入方式。从图中可以看到,槽计数器(vslotcounter)从1开始编号直到用户配置的值。在第一个静态槽实现了媒体接入。

图7是动态段的媒体接入方式。从图中可以看到,周期8的动态段有动态槽计数器zMinislot,从0开始编号直到用户配置的值。在第5个动态槽实现了媒体接入。

结语

本文介绍了基于FlexRay协议的媒体接入控制的设计过程,并进行了设计验证。从仿真结果分析,它符合协议的要求,能够生成通信控制器的时钟周期,将时钟周期进一步划分为4个段,并且给出静态段和动态段的具体媒体接入方式。

评论