一种新型的锁相技术―柔性锁相环路及其控制方案研究

假设三相输入电源电压畸变即电压中含有零序、负序和谐波分量。对于零序,做C32变换后其值为0,对结果没有影响,所以不予考虑。此时的三相电压为 本文引用地址:http://www.eepw.com.cn/article/159956.htm

ua=![]() [U1nsin(nω t+φ1n)+U2nsin(nωt+φ2n)]

[U1nsin(nω t+φ1n)+U2nsin(nωt+φ2n)]

ub=![]() [U1nsin(nωt+φ1n-120°)+U2nsin(nω t+φ2n+120°)]

[U1nsin(nωt+φ1n-120°)+U2nsin(nω t+φ2n+120°)]

uc=![]() [U1nsin(nωt+φ1n+120°)+U2nsin(nω t+φ2n-120°)](4)

[U1nsin(nωt+φ1n+120°)+U2nsin(nω t+φ2n-120°)](4)

式中:下标为1的表示正序,下标为2的表示负序;

n表示谐波次数(当n等于1时表示基波);

U表示电压有效值;

φ表示初相角;

ω为电网电压角频率。

从而可以得到

uq=![]() U1nsin[(n-1)ωt+φ1n]-

U1nsin[(n-1)ωt+φ1n]-![]() U2nsin[(n+1)ωt+φ2n](5)

U2nsin[(n+1)ωt+φ2n](5)

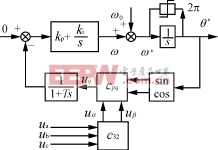

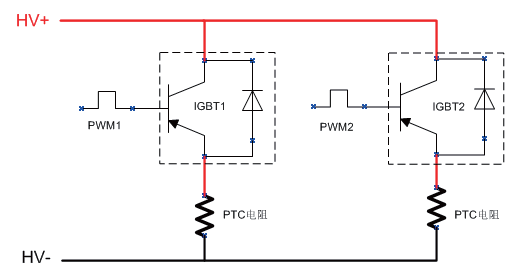

由式(5)可以看出,仅有基波正序转换为直流分量,其他分量经过转换都是频率较高的分量。经过滤波,将这些高频分量滤除,则SPLL的输出就不受负序、零序和谐波的影响。这就保证了在畸变输入电压的情况下,SPLL能够正确地锁定输入电压的基波正序。关于滤波,因系统中存在两个积分环节,对高频分量有较强的抑制作用,所以,一般不需要额外的滤波环节。但是当在三相输入电压严重不平衡时,负序分量很大,若要将其完全滤除,所需时间较长,从而影响系统的动态响应时间。为此,可在pq后加入一个滤波环节来加速负序分量的滤除,如图3所示,从而在保证滤除负序分量的情况下,系统有较短的动态响应时间。

图3 改进的SPLL结构框图

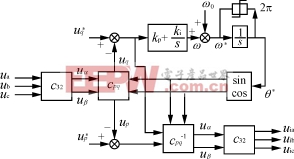

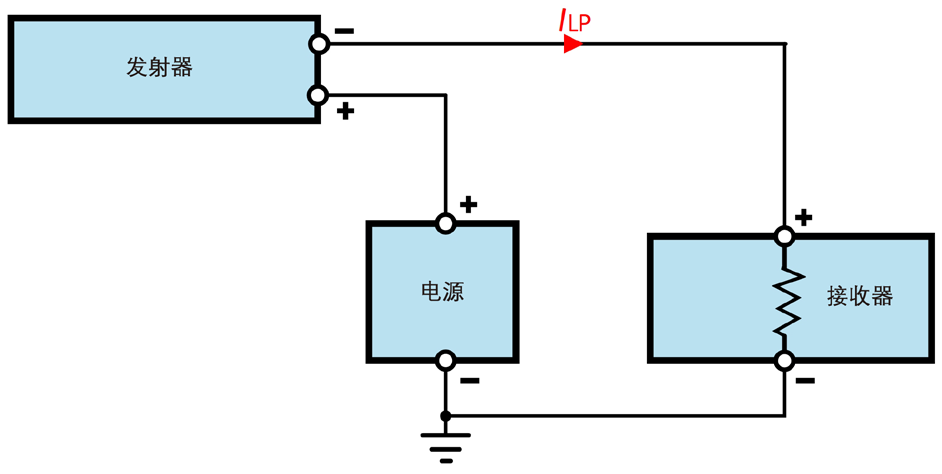

由式(3)可知,uq代表输入电压的相位信息,up代表输入电压的幅值信息。在相位锁定的情况下,前者为零,后者是一仅和幅值有关的直流分量。利用uq构建SPLL达到锁相的目的,而利用up可将理想负载电压转换为一常数和实际输入的电源侧电压经转换后相减,得到有功分量上需要补偿的值,再经反变换即可得到最终的指令。其控制框图如图4所示。

图4 利用瞬时无功获得指令

图4中的上半部分是SPLL,它保证准确的锁定电源侧畸变输入电压的基波正序相位;下半部分是为保持负载电压有恒定的幅值。这种方案对电压的幅值和相位分开考虑,物理意义比较明显。而且,若目标补偿电压的幅值改变,仅须对目标输入up*进行修改,所以比较灵活。如果使用空间矢量PWM调制(SVPWM)就不须对指令进行反变换,从而节省大量资源,该方案就更为适用。

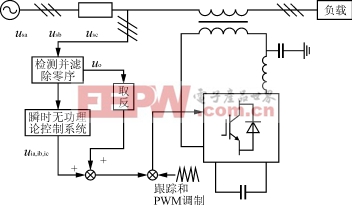

使用这种控制方案,得到DVR的补偿指令,通过三角波比较等跟踪方式控制逆变器的工作,即可达到补偿畸变电压的目的。其流程如图5所示。

图5 DVR工作流程图

评论