基于CMOS图像传感器的视频采集系统设计

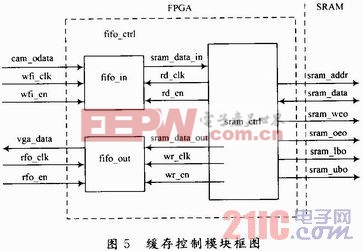

2.4 缓存控制模块

静态随机存储器(Static Random Access Memory,SRAM)和同步动态随机存储器(Synchronous DynamicRandom Access Memory,SDRAM)是目前常用的2种存储器,2种存储器各有优劣,而SRAM相对于SDRAM时序控制较为简单,因此本系统采用SRAM作为数据缓存。缓存控制模块主要实现将转换后的数据缓存在SRAM写FIFO中以及将从SRAM读出的数据缓存在SRAM读FIFO中,而前端数据采集和处理是用OV7670输入的25 MHz的像素时钟作为主控时钟的,而SRAM的读写时钟为100 MHz,而后端VGA控制模块的时钟也为25 MHz,对于数据在异频的时钟域之间的传输,需要利用例化2个异步FIFO模块fifo_in和fifo_out作为数据在不同时钟域之间的缓冲。FIFO通过IP核实现,存储宽度为16 b,存储深度选择512。缓存控制模块的框图如图5所示。利用FIFO解决异频时钟域数据同步的方法是用上级随路时钟写上级数据,然后用本级时钟读出数据。由于时钟频率不同,因此两个端口的数据吞吐率不一致,设计时要开好缓冲区,并通过监控确保数据不会溢出。本文引用地址:http://www.eepw.com.cn/article/159779.htm

2.4.1 fifo_in模块

在本系统中用数据采集与格式转换模块处理后的16位图像数据作为fifo_in模块的输入数据,每次往FIFO中写一行数据(320个16位数据)OV7670输入的像素时钟作为写时钟,行有效cam_href作为FIFO写使能,FIFO的读时钟rdclk为100 MHz,也是SRAM的读写时钟。FIFO读使能产生是通过判断FIFO写使能下降沿来生成一个计数值为320的计数器,在计数期间将读使能置高,将数据由FIFO缓存到SRAM。因为在320个数据写完后有一段时间行有效为低,由于SRAM读速率远大于上一级写速率,可以充分利用这段时间将数据存入SRAM。

2.4.2 fifo_out模块

由于采用单片SRAM,SRAM的读写要避免冲突。因此通过判断fifo_out模块中的wrusedw(FIFO中剩余的数据数量)来控制FIFO的读/写。当wrusedw的值小于192时,将一个标志位fifo_empty置高。为避免读写冲突,将SRAM读使能的产生分为2种情况,在帧有效信号置高期间,此时一帧图像的数据正在由图像传感器输出,SRAM会存在写入数据的情况,只有在fifo_empty置高和SRAM写使能下降沿同时满足的情况下读使能才会置高,而在帧有效信号为低期间,SRAM不会写入数据,只需在fifo_empty置高时一个计数值为320的计数器开始计数,在汁数期间将读使能置高即可。而FIFO的读使能来自VGA控制模块,在需要输出图像数据到VGA显示器上显示时,VGA控制模块读FIFO使能置高,来读取FIFO中的图像数据。

2.5 VGA控制模块

VGA(Video Graphics Array)即视频图形阵列,是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。

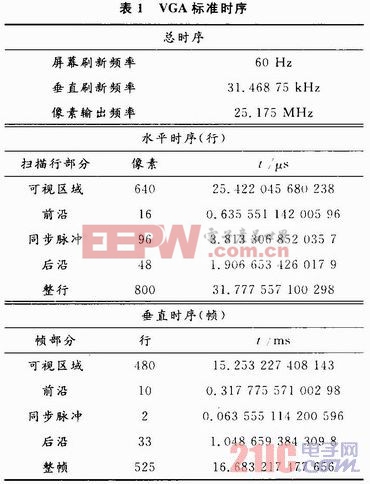

VGA控制模块主要是产生符合要求的VGA时序,使得视频图像数据能够正确地在VGA显示器上进行显示。本系统中VGA控制模块产生的是分辨率为640×480,刷新率为60 Hz的VGA时序,并将从SRAM读出的16位像素信号分成5位red信号、6位green信号和5位blue信号,输出到D/A转换电路。

VGA控制模块中主要利用行同步计数器hcnt和场同步计数器vcnt来分别产生行同步和场同步。时序主要参考分辨率为640×480,刷新率为60 Hz的VGA工业标准时序,如表1所示。

评论